### Ramping New Products Yields in the Deep Submicron Age

ISQED 2000 March 21st, 2000 PDF Solutions, Inc. John K. Kibarian

### **Major Points**

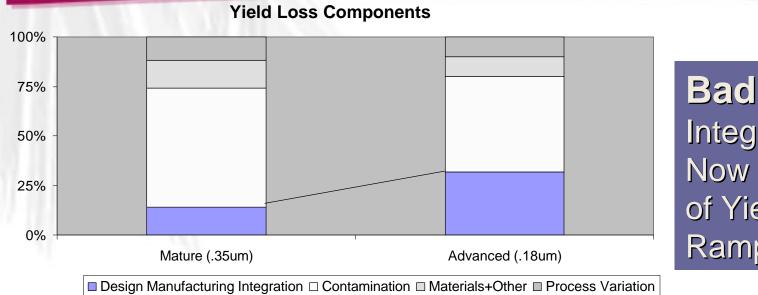

- Increasing design and process complexity becoming critical factor leading to yield loss

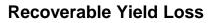

- Systematic yield loss component is significant, growing, and recoverable

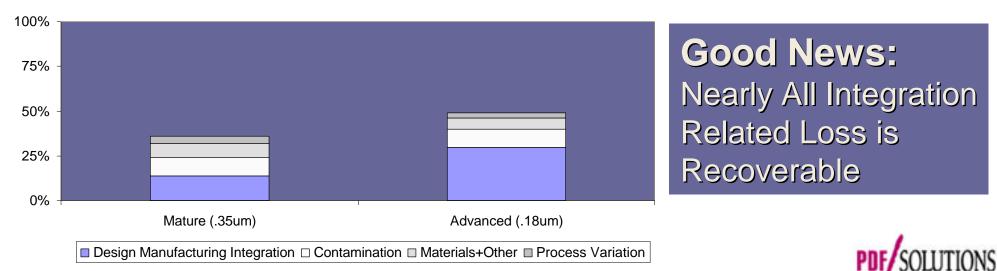

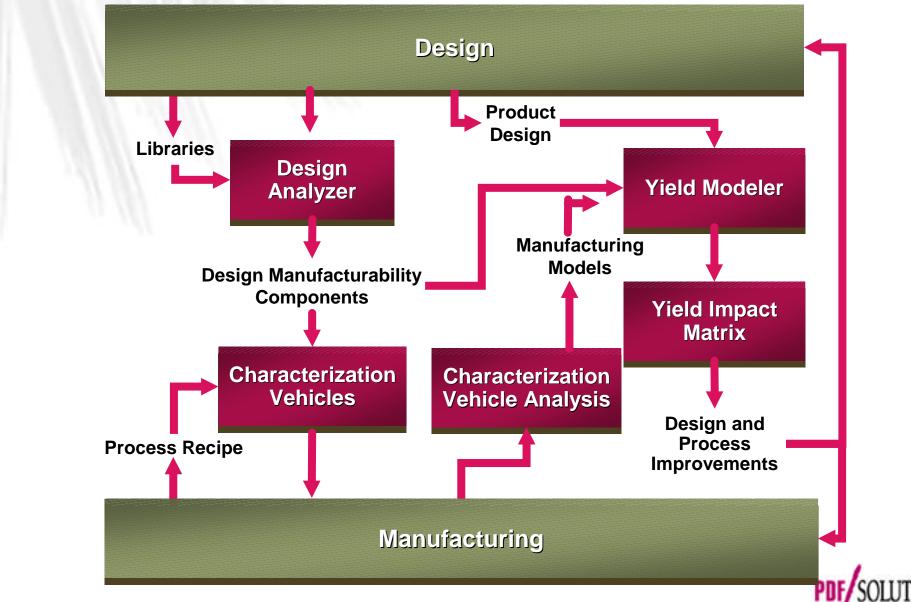

- Fundamental new approach, focused on integration between design, process and manufacturing, is required to recover yield loss

#### Outline

- Product Yield Ramps: the market pressures

- The Design-Manufacturing Integration Problem

- Solution

- Examples

- Concluding remarks

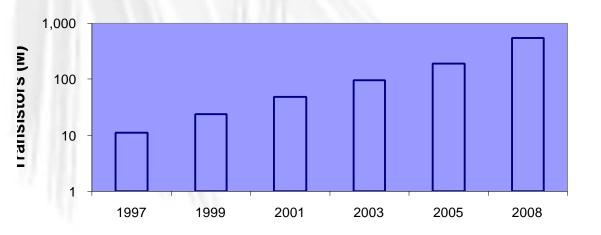

### **Complexity is Increasing Across the Board**

**IC Complexity: Transistors**

IP Reuse is Critical to Get Designs to Market Faster

Unless Corrected, Increased Processing Complexity Reduces Yield up to 5% per Year

#### **IC Complexity: Processing Steps**

PDF/SOLUTIONS

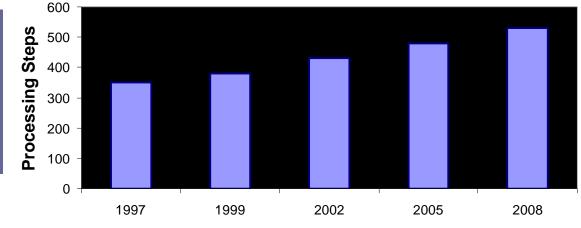

## The Window is Tightening

1001

V AICIO

Years to 1 Million Sales

21-Mar-90 \$5 . PDF Solutions, Inc.

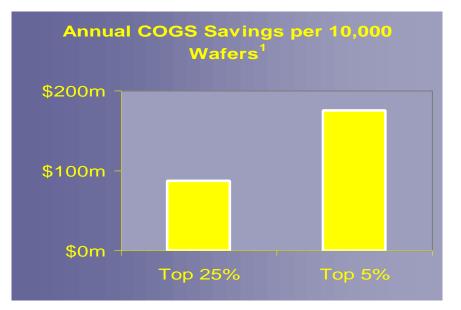

#### **Missing the Window is Expensive**

#### Three costs:

Lost market share

Increased NRE

Increased Costs of Goods Sold (COGS)

## Integration effects market entry point, performance, and cost basis

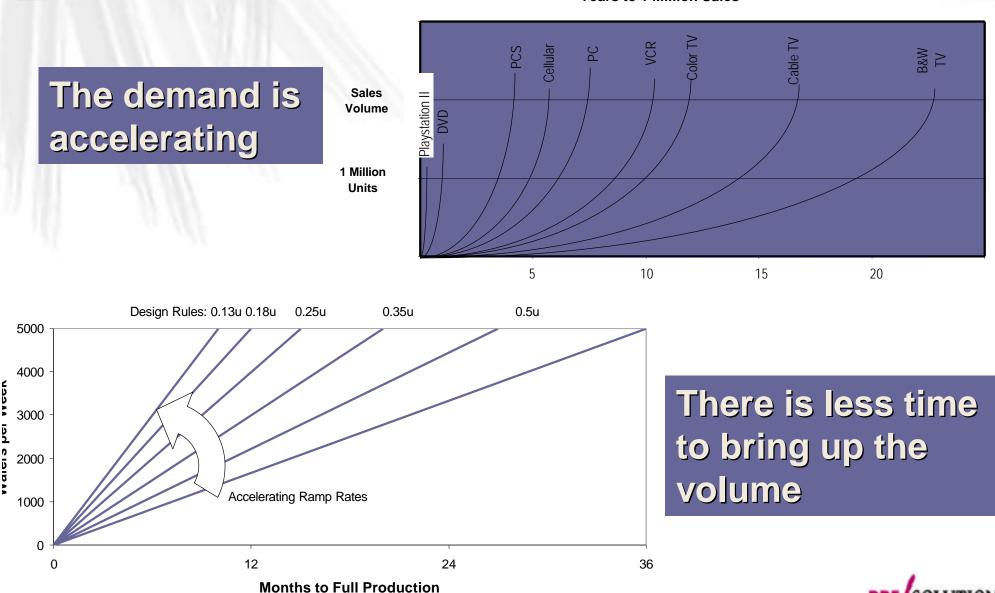

## And Those Yield Loss \$\$\$ are Recoverable ...

#### **Bad News:**

Integration Issues Now Account for 30% of Yield Loss During Ramp

## ... but, an Integrated Approach is Required

"Ask yourself this: Why does a MIPS core cost 25 cents, and you go to QED and there's a 100-fold increase in value? ... the QED part is worth \$25 because it is implemented in silicon."

- Rob Chaplinsky, general partner of Mohr Davidow Ventures

# Technical Issues Have Both Design and Manufacturing Implications

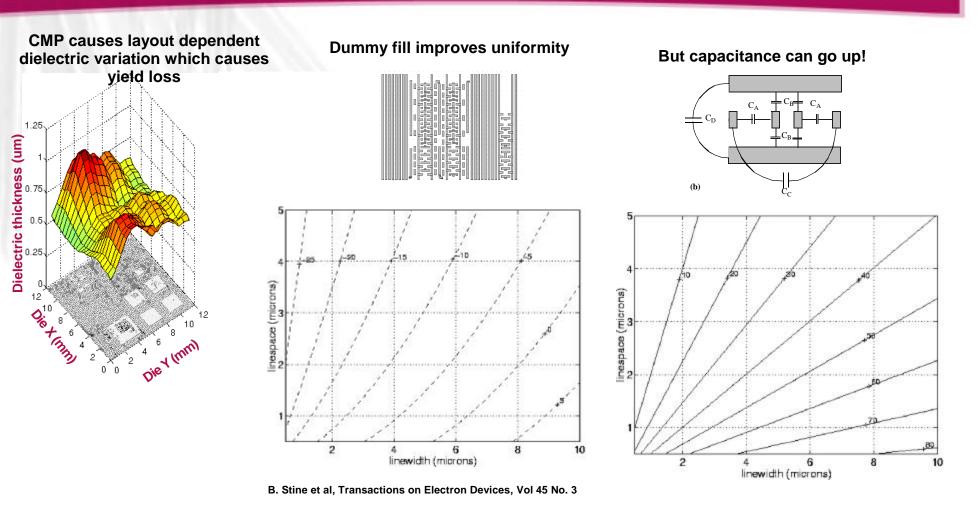

| New Technology                                             | Impact on Design /<br>Manufacturing<br>Interface                                                 | Compensation                                                    | Design –<br>Manufacturing Issue                                                                               |

|------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| Chemical<br>Mechanical<br>Polishing (CMP)                  | <ul> <li>ILD Variability</li> <li>Depth of focus</li> <li>Capacitance<br/>variability</li> </ul> | <ul> <li>Dummy fill</li> <li>Increased design margin</li> </ul> | <ul> <li>What is the circuit performance impact?</li> <li>What is the optimal dummy fill strategy?</li> </ul> |

| I-Line @ 0.35μm<br>DuV @ 0.25μm and<br>below               | <ul> <li>Large w/in chip line<br/>width variation</li> </ul>                                     | <ul> <li>Optical Proximity<br/>Correction</li> </ul>            | <ul> <li>Printability verification<br/>after OPC?</li> <li>Gap fill issues?</li> </ul>                        |

| Channel & Source<br>Drain Engineering<br>RTA, Tox, Poly CD | <ul> <li>Increased relative<br/>variability of<br/>transistor<br/>performance</li> </ul>         | <ul><li>Statistical design</li><li>Increase margins</li></ul>   | <ul> <li>Traditional worst case<br/>corners not valid</li> </ul>                                              |

| Re-use of large<br>design cores                            | <ul> <li>Debugging product<br/>yield issues</li> </ul>                                           | <ul> <li>Black box yield<br/>models</li> </ul>                  | <ul> <li>Fault localization<br/>difficult</li> </ul>                                                          |

## Design or Manufacturing Problem? Both!

21-Mar-00 • 10 • PDF Solutions, Inc.

Optimal solution depends on both design and process considerations

# Simulating Design - Manufacturing Integration

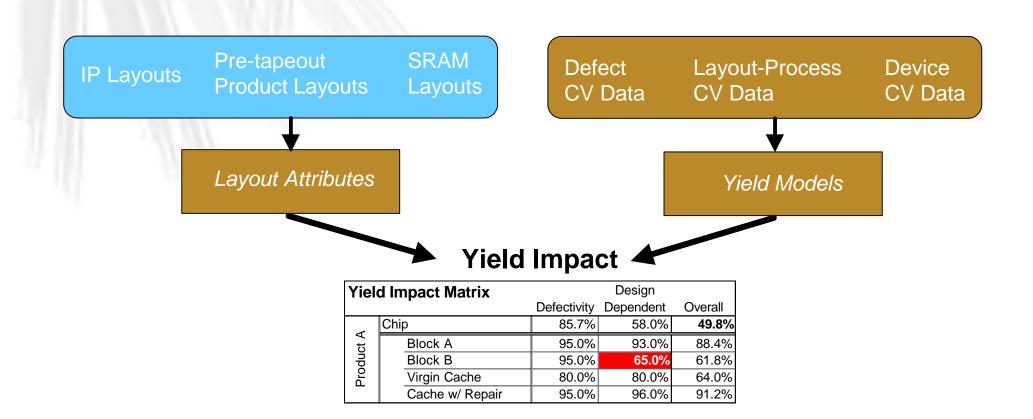

### **The Yield Impact Matrix**

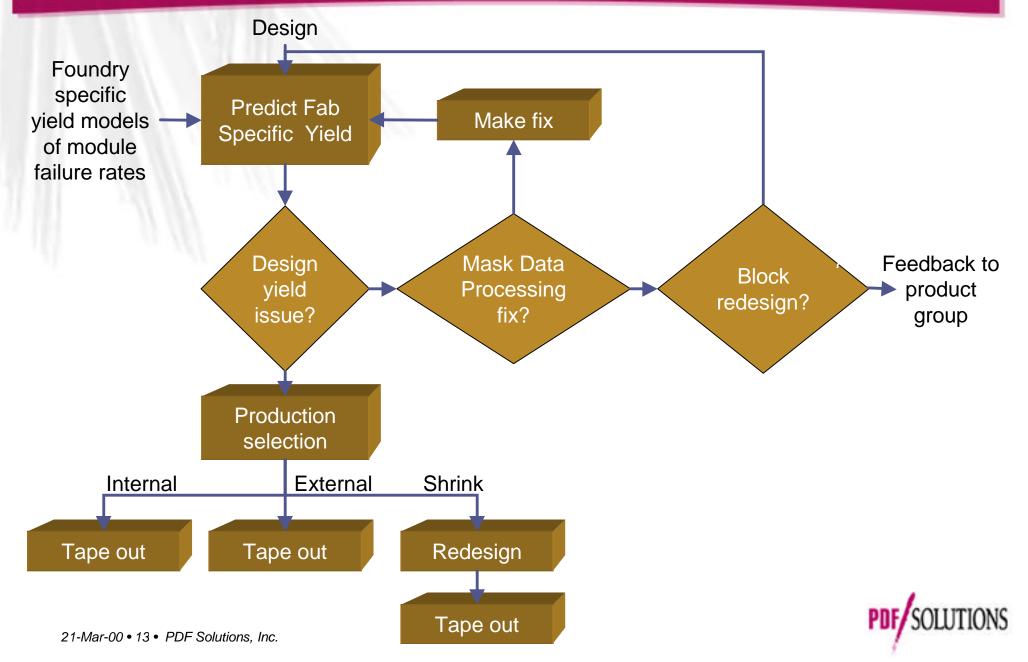

#### Using Simulated Integration Results to Make Production Decisions

#### Example 1: Via Short Flow CV Example Floorplan

| 5        | Long Runners         |            |                         |                  |         |

|----------|----------------------|------------|-------------------------|------------------|---------|

|          | Via1 Loading         |            |                         |                  |         |

| Long Rur | Via2<br>Loading      | Con<br>Loa | itact<br>ding           | Isolated<br>Vias | Long Ru |

| Runners  | Via2<br>Misalignment |            | Contact<br>Misalignment |                  | Runners |

|          | Redundanc            |            | У                       | Size             |         |

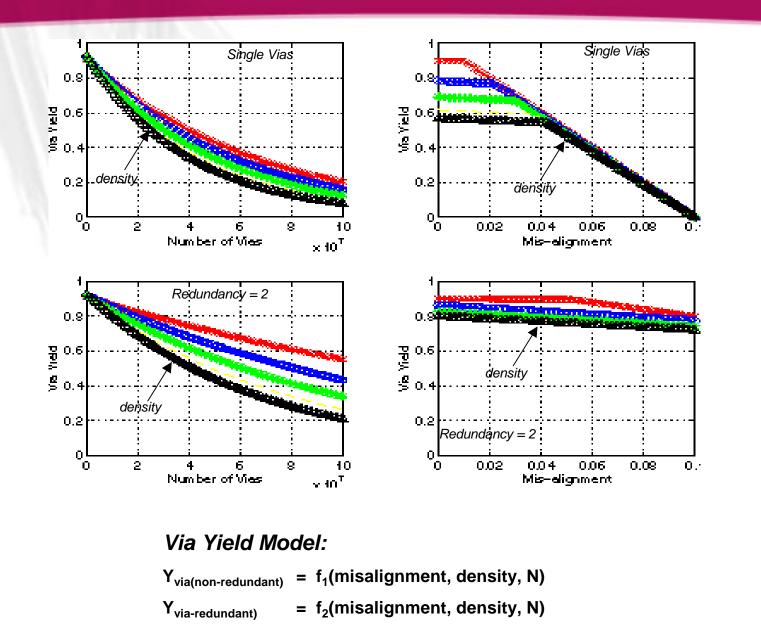

Via1/Via2/Contact Loading: Compute yield impact of density.

- Via2/Contact Misalignment: Compute yield impact of misalignment of via to underlying layers.

- Redundancy:

Compare fault rai

Compare fault rates of single via chains to redundant via chains.

• Size:

Compute yield impact of via size. Check process margin.

• Long Runners:

Compute yield impact of long metal runs in via chain.

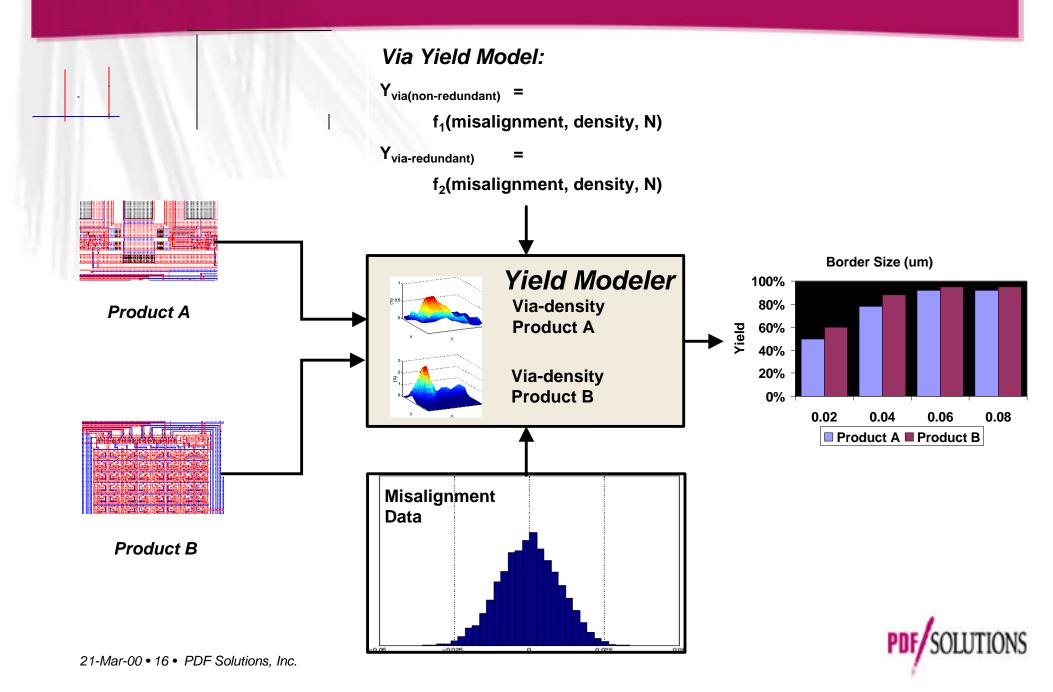

#### **Example 1: Yield Modeling** Process Specific Via Yield Model

#### **Example 1: Design Yield Entitlement** Product Specific Via Yield Prediction

#### Example 2: Optimizing Fill For Performance and Yield

**Questions about dummy fill algorithm:**

- Which layers?

- What pattern?

- Should you exclude sections of the design layout?

#### Approach

Build vehicle to characterize performance/yield dependencies on layout choice

- Build yield models

- Optimize dummy fill for product chips

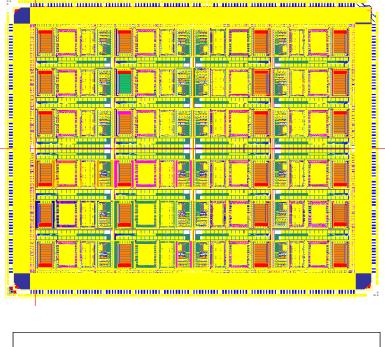

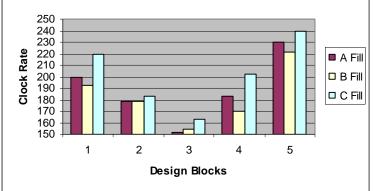

#### Example 2: Optimizing Fill for Yield and Performance

#### **30 Identical circuits**

• Each contains: SRAM, gate dependent and interconnect dominated logic circuits, and analog blocks

Each variant is a DOE element exploring dummy fill, meta/poly OPC, via sizing options

Some fill patterns have positive impact on yield and performance for some design blocks

### **Concluding Remarks**

- Increasing design and process complexity becoming critical factor leading to yield loss

- Systematic yield loss component is significant, growing, and recoverable

- Fundamental new approach, focused on integration between design, process and manufacturing, is required to recover yield loss