### Beyond 28nm: New Frontiers and Innovations in Design For Manufacturability at the Limits of the Scaling Roadmap

Luigi Capodieci, Ph.D. DFM Director - R&D Fellow

# Outline

<u>Challenges</u>

- Variability and the Limits of IC Geometrical Scaling

- Methodology Innovation in Design for Manufacturing Solutions

- Advanced Rule-Based Verification (Yield Analysis and Yield Enhancement)

- Novel Flow: DRC+

- 2D Shapes Pattern-Matching Based Physical Design Verification

- Model Accuracy and Full-Chip Performance without Compromise

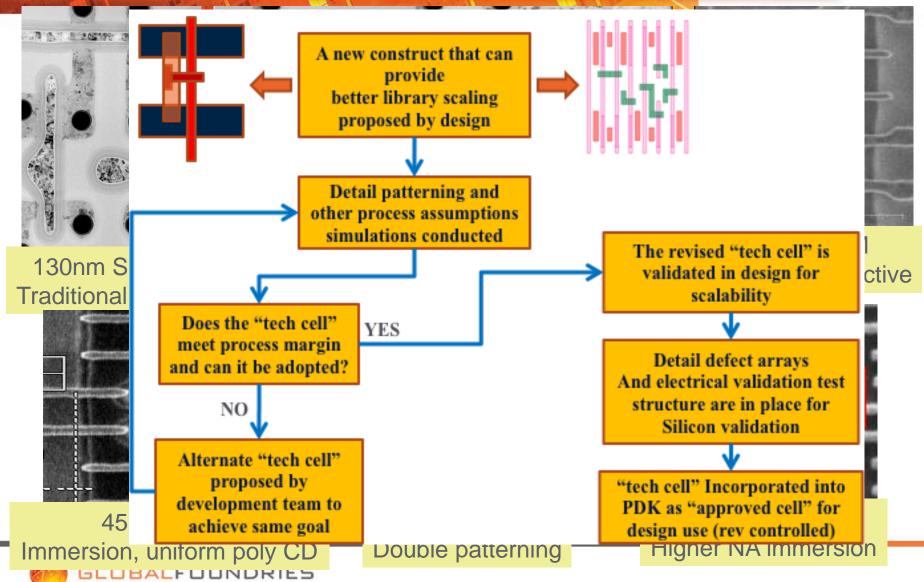

- Si-Accurate Model-Based Printability Verification: enabling special 'tech-cell' constructs

Manufacturing: closing the variability loop

- Design-Enabled Manufacturing:

- Faster Yield Ramp and Foundry Customer Value

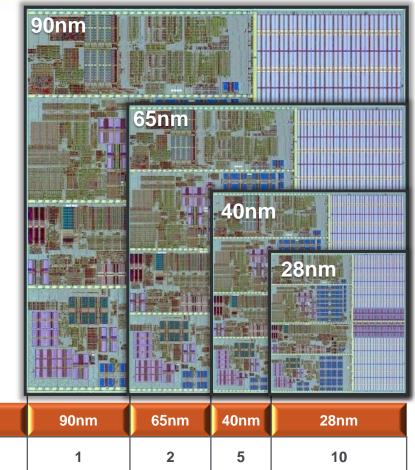

### IC Integration State of the Art (today) Scaling and Device Density

#### **Gate First HKMG**

Process

**Device Density**

- 28nm "Gate First" provides true scaling (relative to 40nm)

- 1. ~100% density increase

- 2. Up to 50% increased speed and 50% reduction in energy/switch

- Sustains 40nm Layout Style Advantages: Bi-directional Poly, Poly Jogs, Large Caps

- 10-20% Smaller Die Relative to 28nm "Gate Last"

0.6

1

0.36

0.22

Normalized Power per gate

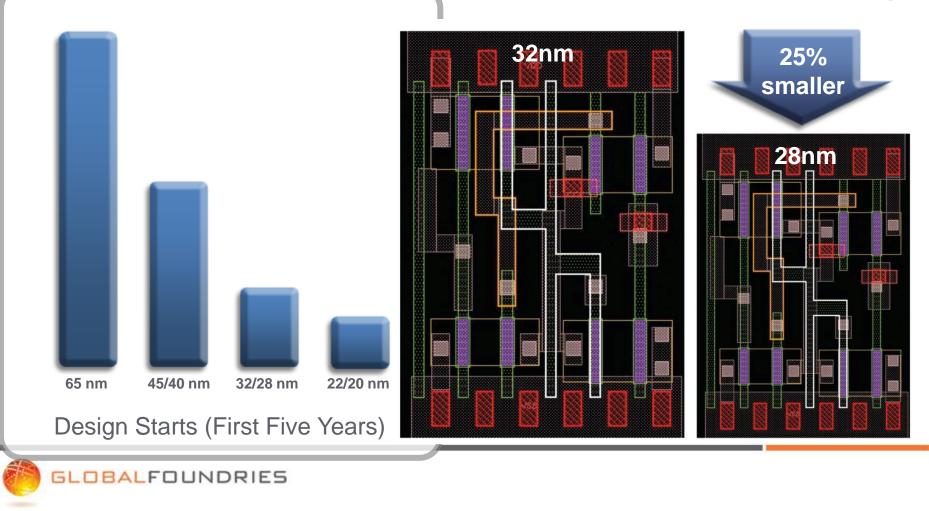

### Key Technology Parameters: Innovation and Time-to-Volume

Number of tape-outs is decreasing ...

...but advanced technology continues to drive innovation, provide new value and volume is increasing

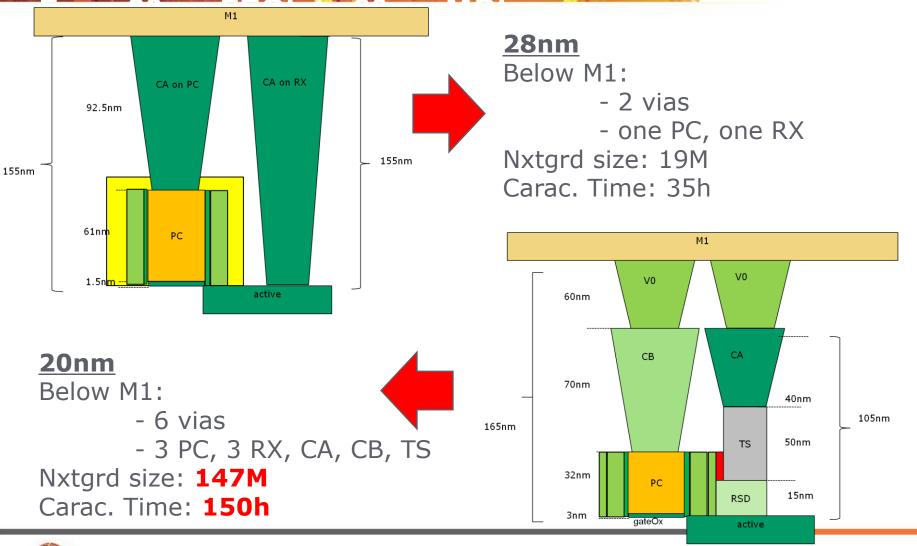

### 20nm: Scaling and Integration Continue

| 90nm |                              |      |      | r    |      |      |

|------|------------------------------|------|------|------|------|------|

| 65nm | Process                      | 90nm | 65nm | 40nm | 28nm | 20nm |

| 40nm | Device Density               | 1    | 2    | 5    | 10   | 20   |

| 40mm | Normalized<br>Power per Gate | 1    | 0.6  | 0.36 | 0.22 | 0.14 |

|      |                              |      |      |      |      |      |

#### **Disruptive Transition: New Integration Schemes**

GLOBALFOUNDRIES

### **Tomorrow's Lithography: Tomorrow**

#### **Extreme Ultraviolet (EUV)**

- Continuing to drive collaborative R&D

- Early era:1990-2000

- Founding member of EUV LLC

- Demonstrated fundamental capabilities

- Today: 2001-2010

- 2008 SPIE: first full-field EUV patterning on 45nm test chip

- >60 EUV masks shipped by Dresden mask house

- Leading efforts to address

Line Edge Roughness (LER)

- Tomorrow: 2012-14 and beyond

- Will be one of early customers for production-level EUV tools

EUV mask produced at AMTC

Alpha Demo Tool at CNSE Albany

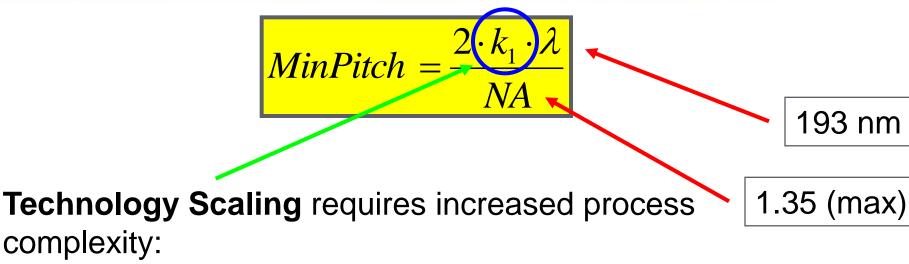

### Lithographic Scaling Limits

i.e. reduction in  $k_1$  factor (theoretical min=0.25)

#### **Computational Technology Scaling:**

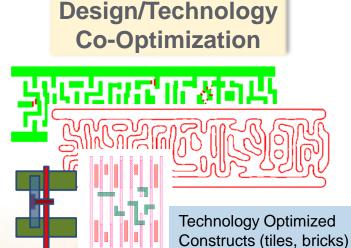

Systematic reduction of  $k_1$  factor by rigorous <u>**Co-Optimization**</u> of:

(1) Physical Design (Layout, Design Rules, Place and Route)

(2) Process (Illumination, Lithography, Mask RET, OPC, etc.)

Computational Scaling is also known as: Design-Process-Technology Co-Optimization

### From 28 to 20nm Enablement: SMO Source-Mask Optimization

#### Algorithm:

Optimize illumination source parameters based on a library of layout features (1D, 1.5D, 2D)

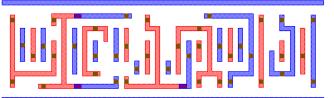

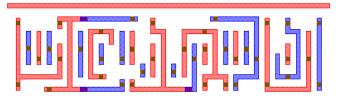

### 20nm Enablement: Double Patterning and Layout Decomp

- Double Patterning to pattern sub 80nm features

- Decomposition tools and algorithms

Stitching

Single direction gate restriction:

• Special constructs (managed DRC violation) to maintain scale factor

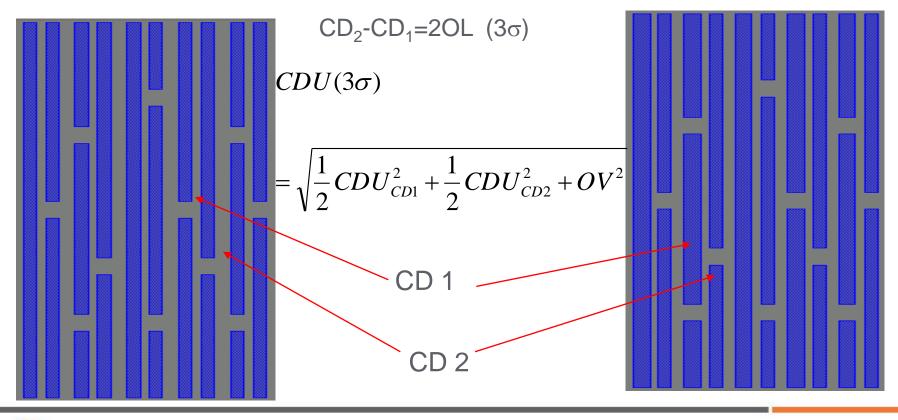

### Double patterning: Overlay Implications

Overlay can cause local line width variations or local space CD variation depending on process scheme, which is translated into electrical performance degradation:

Gate with variation, gate length variation, resistance variation, capacitance variation

### Double patterning: Stiching Implications

- Stitching denotes multiple colors on a single line

- Allows for tighter designs and less coloration conflicts

- Stitching presents challenges for LVS/PEX

- Fuzzy region where 2 neighboring lines could be like or different colors

- Stitch is generated virtually

- Possible resistance issues due to stitch

- At the point of merging between the 2 colors on the same line

- Mis-alignment impact on resistance

- How to model for resistance?

- PEX tool would need to know location of stitch

### **Retargeting (Physical Design)**

- Retargeting denotes the operation of taking physical design shapes provided by the designer and turning them into "target shapes".

- Motivation for retargeting functions in PEX

- Decreased Complication For Designers

- Improved Extraction run-time

- Support of all input types, including GDS and LEF/DEF

- Common PEX tech files for transistor and cell level extractions

- Possible accuracy and simulation run-time improvements

- Motivation for retargeting functions in LVS

- Remove need for separate module

- Eliminate issues caused by integrating separate module with LVS

- No special license requirements

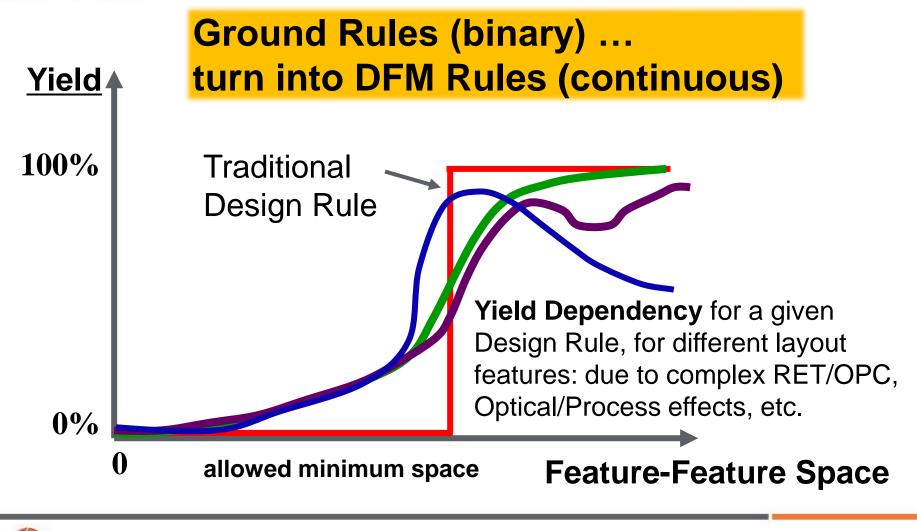

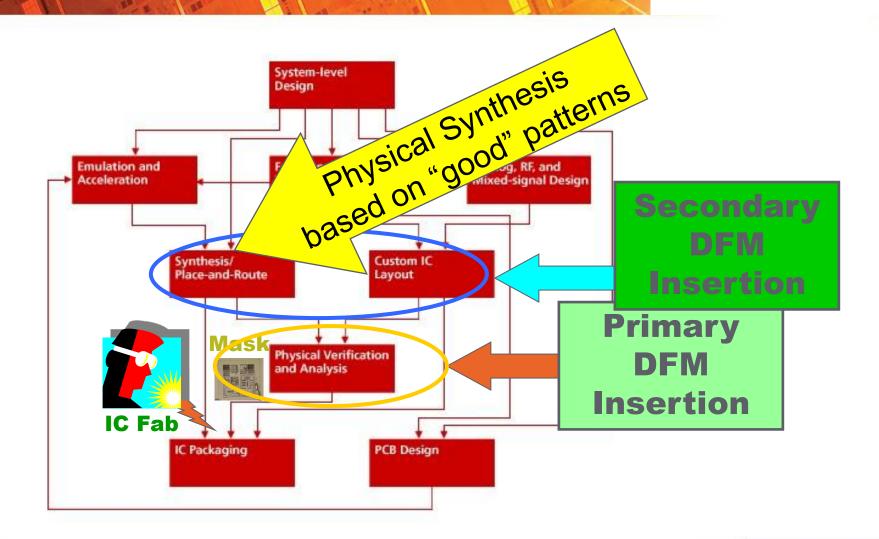

### Managed Variability through DFM

DFM brings manufacturing *variability awareness* into design through EDA tools enablement

- Advanced Rule-Based Verification (Yield Analysis/Scoring and Automated Yield Enhancement)

- Novel Flow: DRC+

- 2D Shapes Pattern-Matching Based Physical Design Verification

- Model Accuracy and Full-Chip Performance

- Seamless Integration in P&R Flow

- Si-Accurate Model-Based Printability Verification with Applications to Special Constructs (tech-cells)

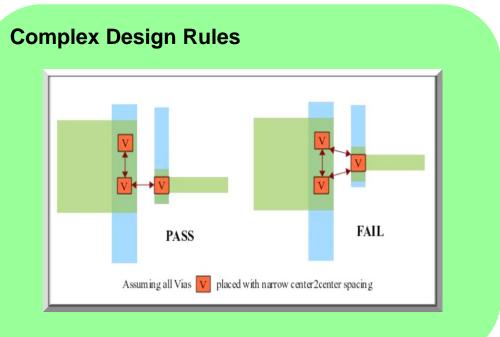

### **Physical Verification: Beyond Design**

#### Traditional Geometrical Design Rules

Set of **geometrical constraints**, necessary to guarantee yield, defined over polygonal shapes and edges in the layout

The Design Rule Manual mediates among: •DESIGN •TECHNOLOGY •FAB

Two Types of DR:1. Restrictive (95%)2. Prescriptive (5%)

### At 28nm and below: Physical Design dependent Yield

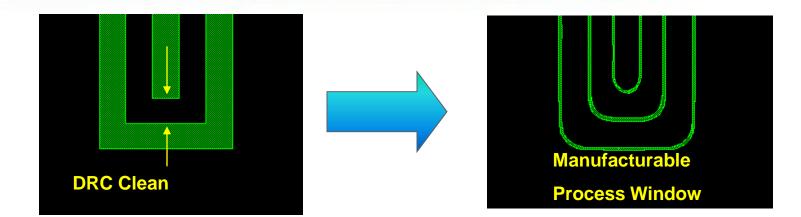

### At 28nm, 20nm and below: Si-Accurate Model-Based Verification is needed

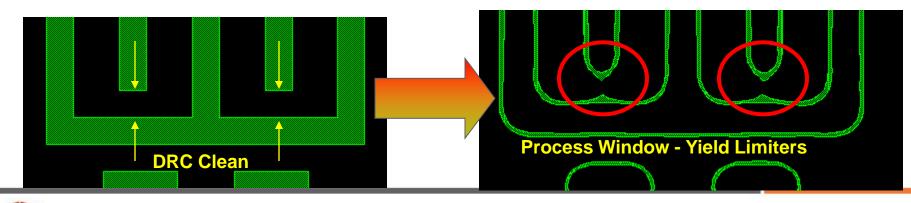

### Model-Based Printability Verification for DRC clean physical design

### Rule-Based DFM: Analysis/Scoring and Enhancement

Typical Recommended Rule results in DRC difficult to analyze and fix MAS/YES quickly identifies and fixes high impact DFM Rule violations

| 1   |       |            | x 2 x  |               |                   |

|-----|-------|------------|--------|---------------|-------------------|

| 1.1 |       | _          |        |               |                   |

|     | 12: 1 | 4          |        | -             | 12.               |

|     | 14    |            | 4      |               | 5                 |

|     | 14. 2 |            |        | 1             | 1                 |

|     | 12.8  | 13         |        | 10            | 5.5               |

|     | 12.3  | A CONTRACT |        | 10 10 1 1     | <u>.</u>          |

|     | Sug!  | 12 6       | 12.    | $\mathcal{L}$ | н <u>с</u>        |

|     | 120   | 14. 15     | 100    | 4 2           | £.                |

|     | de    | A          | S. Cat | 4.5           | $r \sim 10^{-10}$ |

| roup     |                    | DFM R                | ule            | MAS Score                                |

|----------|--------------------|----------------------|----------------|------------------------------------------|

| Eile Ver |                    | <u>Window S</u> etup | ) Cell Summary | Hel<br>idow Suymary                      |

| View -   |                    | Total_Quality        | 0 Rows: *      | 12 12 Filter                             |

| Туре     | Group              | Rule Name            | MAS_To         | tal_Quality 🛆                            |

| mas28gf  | Yield_Margin       | 611cR_V1             | 0.943832       |                                          |

| mas28gf  | Yield_CriticalArea | 2x01aR_B1            | 0.942830       |                                          |

| mas28gf  | Yield_CriticalArea | 52R                  | 0.916912       |                                          |

| mas28gf  | Device_Variability | 713R                 | 0.847574       |                                          |

| mas28gf  | Yield_Redundancy   | 16X62R               | 0.804593       | i                                        |

| mas28gf  | Yield_Redundancy   | 2×66R_W0             | 0.804593       |                                          |

| mas28gf  | Yield_Redundancy   | 8x60_YSaR            | 0.804593       | i                                        |

| mas28gf  | Yield_Redundancy   | 8x60_ZVaR            | 0.804593       | i la |

| mas28gf  | Yield_CriticalArea | 601aR_M2             | 0.746212       |                                          |

|          | Yield_CriticalArea | 501aR                | 0.741389       |                                          |

| mas28gf  | ricia_citacarrica  |                      |                |                                          |

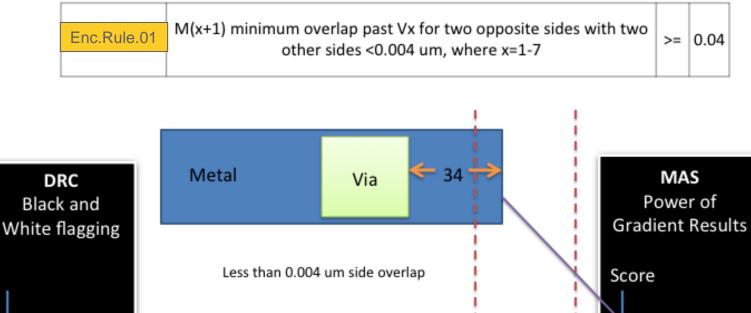

$M\,(x+1)$  minimum overlap past Vx for two opposite sides >= 0.04um with the other two sides < 0.004 um, where x = 1-7.

- MAS: An equation based tool to help designers to quickly analyze their design for usage of recommended rules, and prioritize fixes for the highest impact violations.

- YES : Seamless auto-application of recommendations without impacting current design within existing area

### **Equation-Based Scoring**

#### EXAMPLE: Enclosure Rule

Metal

Fail

Pass

Rule Value

Luigi Capodieci, Ph.D. - Director DFM

Via

38

GR

I

RR

0

Rule Value

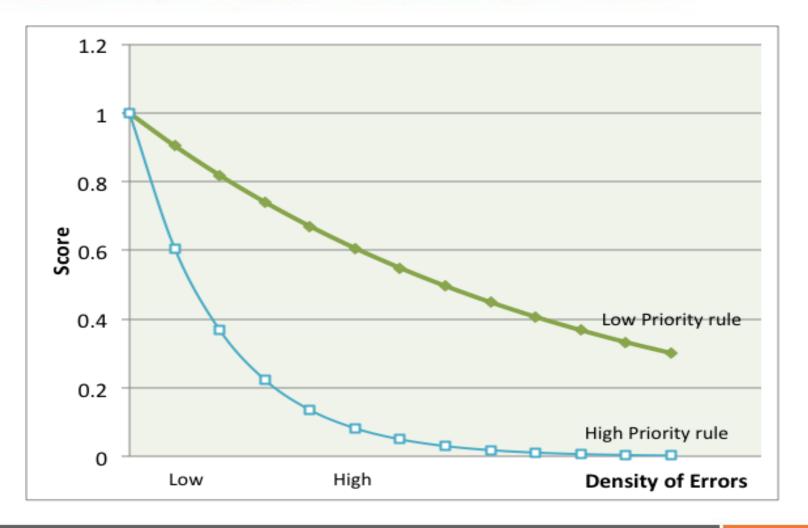

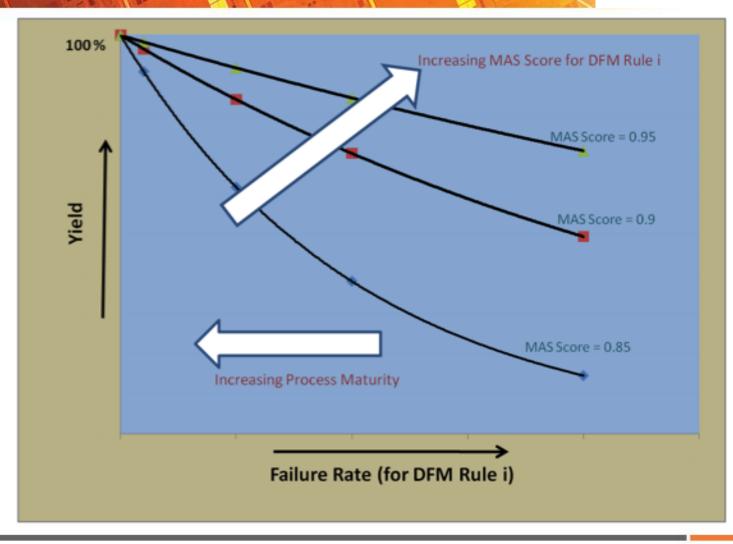

### **Scoring Model for DFM Rules**

### **Score correlation with Yield**

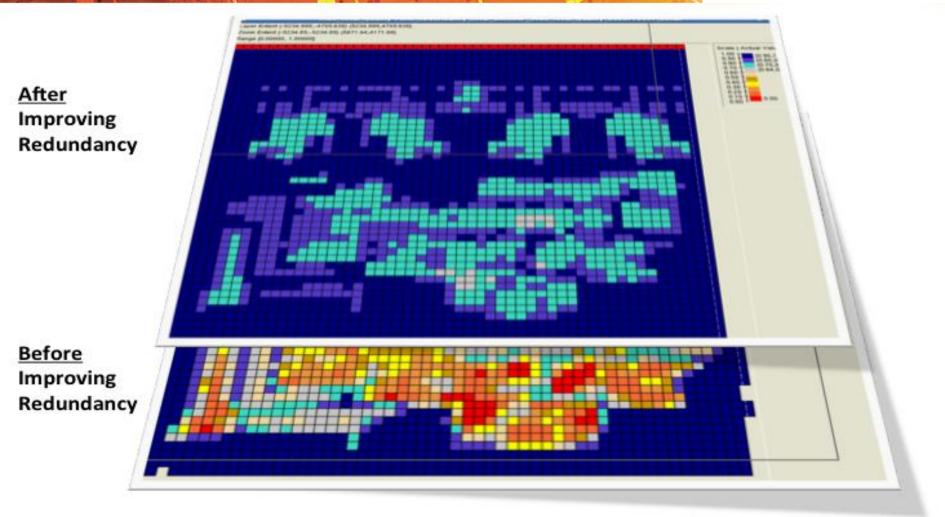

### Full-Chip Solution: Automated Deployment of DFM Rules

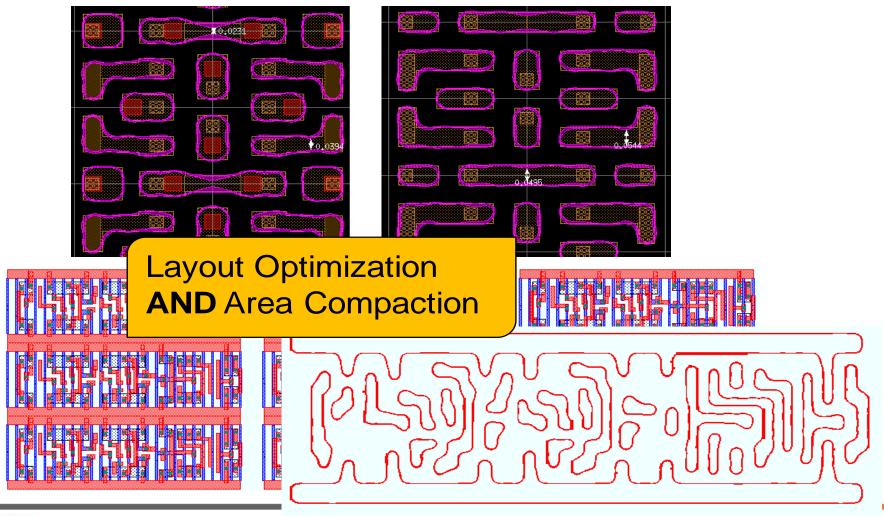

### Model-Based DFM (Printability) drives Layout Optimization/Compaction

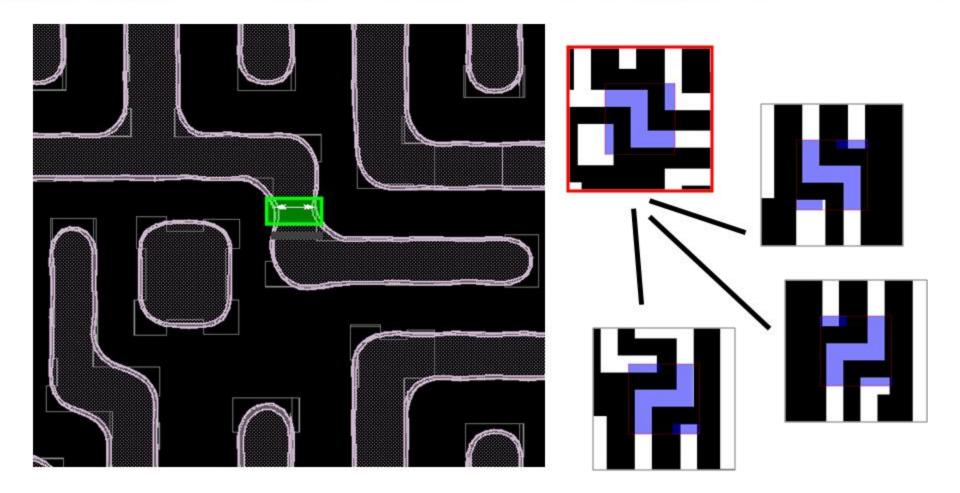

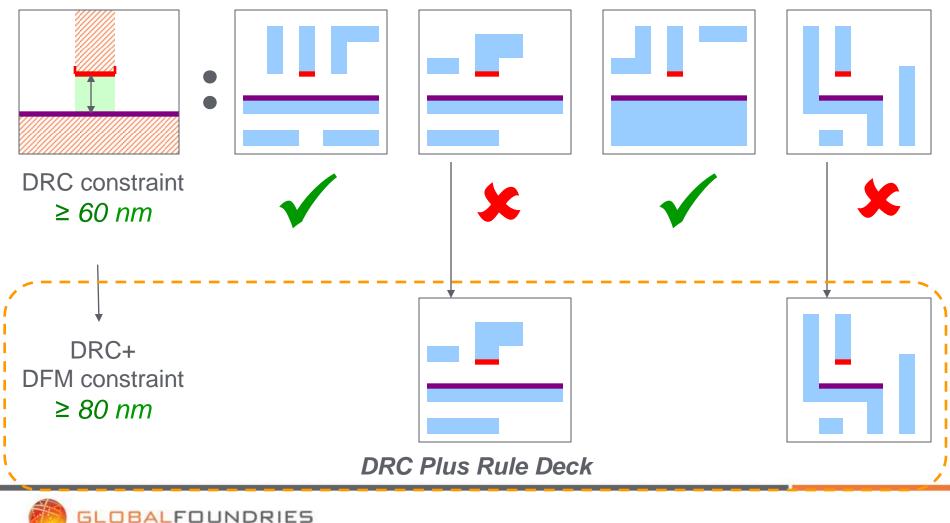

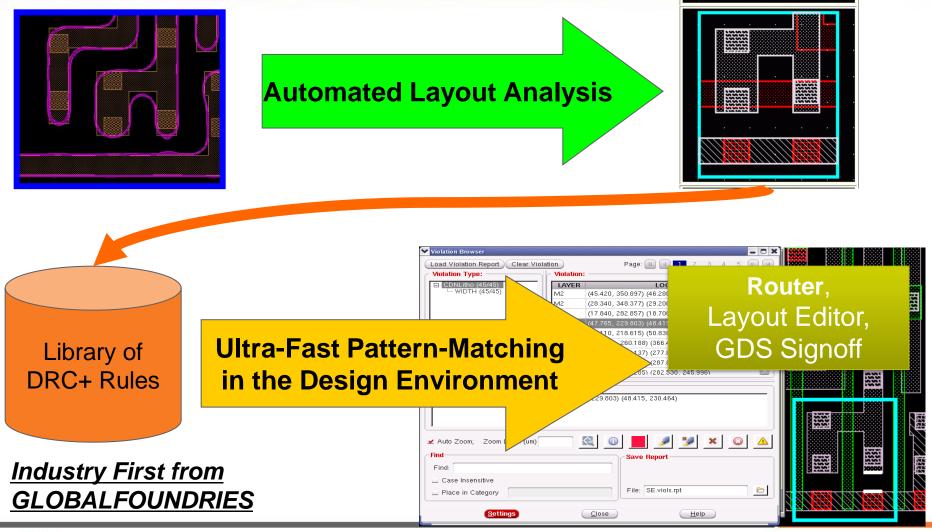

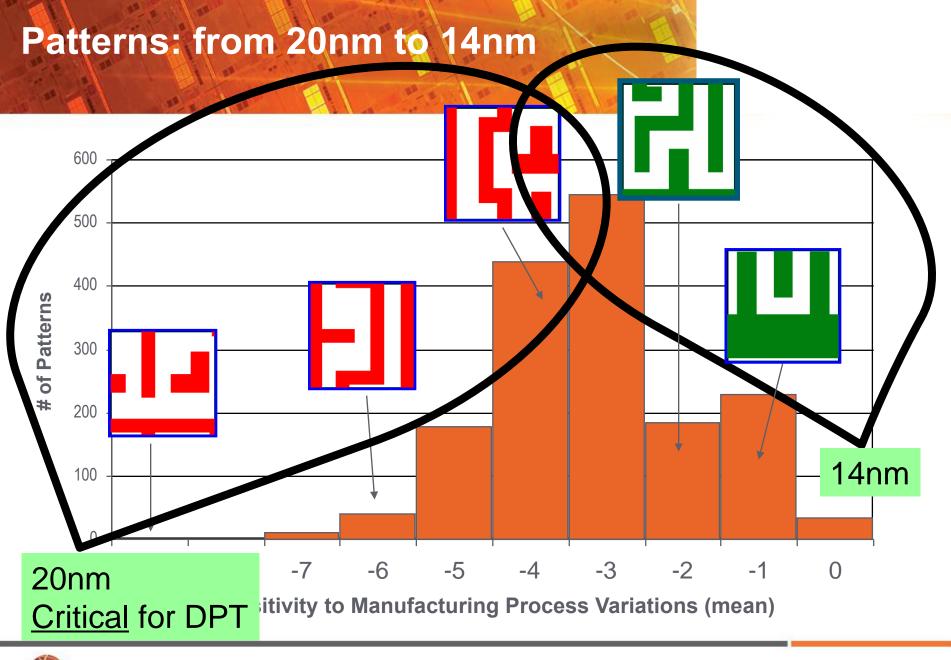

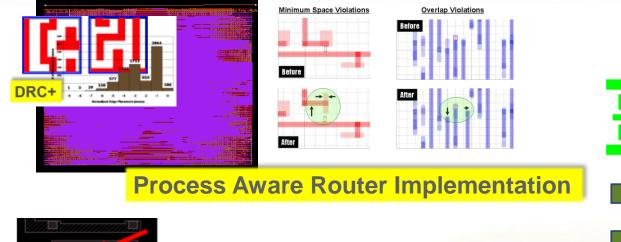

## DRC+: Based on 2D Shapes Pattern-Matching: 10,000X Faster than Simulation

# Configurations + Patterns = DRC+ Rules

#### Configuration: tip-to-side

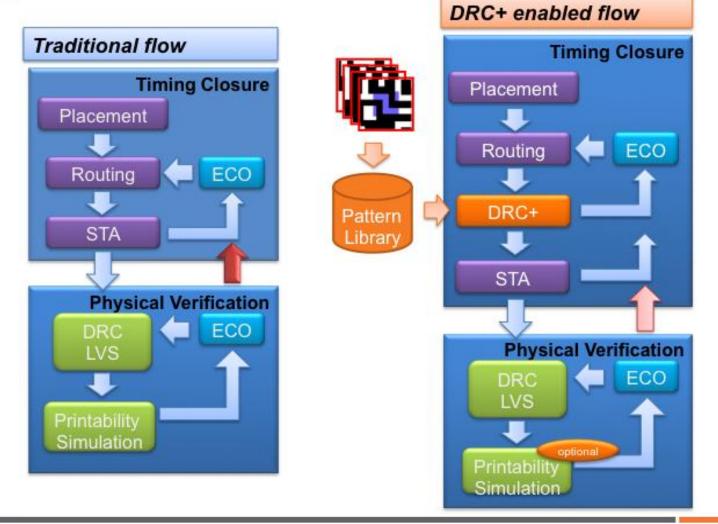

### Integration in P&R Implementation Flow

### DFM Physical Verification in Timing Closure Loop

### **DRC+ Results on Sample Designs**

| Design               | Α     | В     | С     | D      | Е      | F     | G     | н     |

|----------------------|-------|-------|-------|--------|--------|-------|-------|-------|

| Chip Size (mm^2)     | 0.024 | 0.033 | 0.240 | 0.309  | 0.464  | 0.027 | 0.036 | 0.032 |

| Core Size (mm^2)     | 0.023 | 0.031 | 0.115 | 0.294  | 0.440  | 0.026 | 0.035 | 0.030 |

| Std Cell Density     | 85%   | 68%   | 56%   | 95%    | 64%    | 76%   | 60%   | 93%   |

| Instance Count       | 17983 | 18581 | 83539 | 294572 | 303299 | 13577 | 14077 | 34234 |

| Hotspots Detected    | 11    | 8     | 35    | 193    | 135    | 0     | 1     | 9     |

| Hotspots<br>Per mm^2 |       |       |       |        |        |       |       |       |

| (Normalized)         | 475   | 259   | 306   | 658    | 307    | 0     | 29    | 297   |

- Consist of designs such as: CPU design and JPEG

- Different density, instance count and size

- Average of 291 hotspots per mm<sup>2</sup> detected

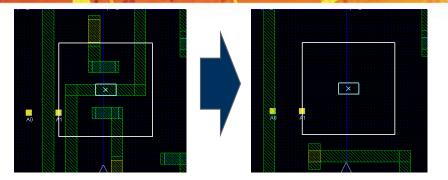

### **Automated Fixing and Timing Closure**

|                             |         | А              | В  | С  | D   | Е   | F   | G | н  |

|-----------------------------|---------|----------------|----|----|-----|-----|-----|---|----|

|                             |         | Hotspots Found |    |    |     |     |     |   |    |

| Auto-Fix                    | 1       | 11             | 8  | 35 | 193 | 135 | 0   | 1 | 9  |

| Iterations                  | 2       | 0              | 0  | 0  | 1   | 0   | -   | 0 | 0  |

|                             | 3       | _              | -  | -  | 0   | -   | -   | _ | -  |

| Max Timing Del <sup>-</sup> | ta (ps) | 43             | 19 | 5  | 48  | 23  | N/A | 3 | 45 |

- 100% of DRC+ hotspots auto fixing with 2 iterations

- Timing delta after fix is significant enough to affect timing closure

- Essential to include DFM physical verification & fixing in timing closure

### Variability Management Without Perfomance trade-offs

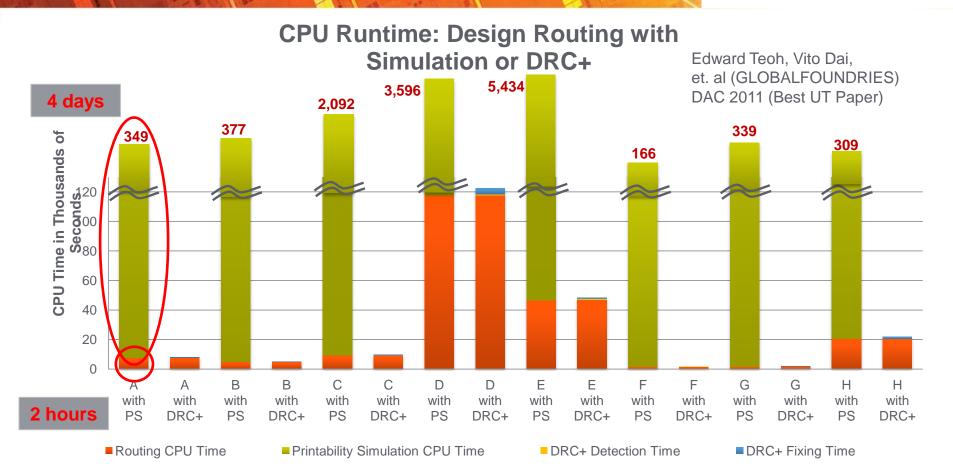

DRC+ is over 10,000 times faster than printability simulation

DRC+ detection and fixing adds very little to the overall routing runtime

### Fine-tuned Design-Technology Co-Optimization: Critical at 20nm!

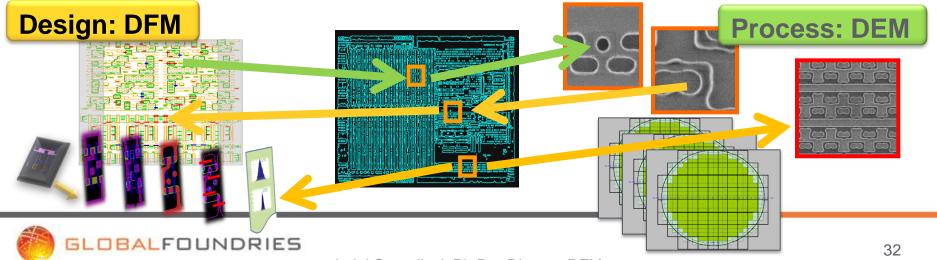

### **DFM: Design For Manufacturing DEM:** Design-Enabled Manufacturing

- DFM and DEM are 2 complementary set of methodologies, which mirror one another by tightly coupling flows in the design space with process metrology and yield data in the manufacturing space.

- **DFM** provides **process awareness into the design cycle** through accurately calibrated models and novel verification flows (DFM sign-off).

- **DEM** enables manufacturing/design co-optimization, using automated physical design analysis and characterization which in turn drive process optimization fine-tuned to specific customer product designs.

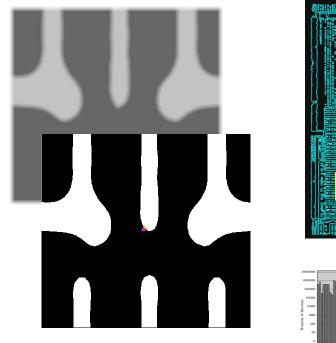

### Pattern-Matching supports Design-Enabled-Manufacturing

Binary Bitmap from SEM Image

### **Evolution of DRC+ and Pattern Matching: Manufacturable-by-Construction Layouts**

## Conclusion: Variability Management fully deployed for 28 and 20nm desig

**Rule-Based DFM**

#### Layout Decomposition Aware Physical Verification

###

## Acknowledgments:

### GLOBALFOUNDRIES Team (insert names) Synopsys Team (insert names)