# Final Program

2023 24<sup>th</sup> International Symposium on

# QUALITY ELECTRONIC DESIGN

April 5-7, 2023

Seven Hills Conference Center

San Francisco State University

San Francisco, CA USA

International Society for Quality Electronic Design Copyright© ISQED. All rights reserved. www.ISQED.com

### **Corporate Sponsors**

# SYNOPSYS® Silicon to Software

### **Technical Sponsors**

ISQED'23 is produced and sponsored by the International Society for Quality Electronic Design Copyright © 2023 All rights reserved

## **WELCOME TO ISQED'23**

### Greetings,

On behalf of the ISQED conference and technical committees, we are thrilled to welcome you to the 24th anniversary of the International Symposium on Quality Electronic Design, ISQED'23. After several years of virtual events due to the COVID pandemic, we are excited to announce that this year's event will be held in-person at the Seven Hills Conference Center, located in San Francisco State University, 800 Font Blvd, San Francisco, CA 94132.

For over two decades, ISQED has been the leading voice and pioneer in the field of Quality Electronic Design (QED). With the increasing complexity of semiconductor technology and design, it is more essential than ever before to follow QED and its underlying principles. ISQED'23 aims to lead the community in this direction with an extensive program consisting of keynotes, panels, tutorials, and over 100 peer-reviewed articles.

This year, the conference will be conducted virtually, with the technical sponsorship of the IEEE Electron Devices Society, the IEEE Circuits and Systems Society, IEEE Reliability Society, and in-cooperation with ACM/SigDA. Conference proceedings and papers will be published in IEEE Xplore digital library and indexed by Scopus.

ISQED'23 is organized around critical trends in Al/ML, Autonomous Vehicles, Security, IoT, and Quantum Computing. The conference program includes two keynote speeches, two embedded tutorials, a panel discussion, and numerous peer-reviewed technical papers that focus on these timely topics.

We are delighted to report that the number of quality papers submitted to the conference this year has been overwhelming. The two and a half-day technical program features four parallel sessions and over 100 peer-reviewed papers highlighting the latest trends in electronic circuit and system design and automation, testing, verification, sensors, security, semiconductor technologies, cyber-physical systems, and more.

All technical presentations, plenary sessions, panel discussions, tutorials, and related events will take place in hybrid format on April 5-7, at Pacific Daylight Time (PDT).

We would like to take this opportunity to express our gratitude to the corporate sponsors of ISQED'23: Synopsys and Innovotek for their invaluable financial support of this conference.

General Chair Sara Tehranipoor West Virginia University

Special Sessions Chair

Hossein Sayadi

California State University, Long Beach

**Tutorials Co-Chair Xiaolin Xun** Northeastern University

Publication Chair Paul Wesling Hewlett Packard (retired) Program Chair Cindy Yi Virginia Tech

Special Sessions Co-Chair Mimi Xie The University of Texas at San Antonio

**Panels Chair Tosiron Adegbija,** University of Arizona

ISQED Founder & Chair Ali A. Iranmanesh Silicon Valley Polytechnic Institute **Program Co- Chair Deliang Fan**Arizona State University

**Tutorials Chair Vita Pi-Ho Hu** National Taiwan University

**Panels Co-Chair Fareena Saqib** University of North Carolina

# **ISQED'23 Best Papers**

### 2A.3

### DC-Model: A New Method for Assisting the Analog Circuit Optimization

Yuan Wang, Jian Xin, Haixu Liu, Qian Qin, Chenkai Chai, Yukai Lu, Jinglei Hao, Jianhao Xiao, Zuochang Ye, Yan Wang Tsinghua University, Beijing, China

### 6A.1

# An Area Efficient Superconducting Unary CNN Accelerator

Patricia Gonzalez-Guerrero, Kylie Huch, Nirmalendu Patra, Thom Popovici, George Michelogiannakis

Lawrence Berkeley National Laboratory, Berkeley, USA

Authors of best papers are acknowledged during the morning plenary session on Wednesday April 5. ISQED'23 best papers are sponsored by Innovotek Inc.

# **ISQED'23 Organizing Committee**

**General Chair Sara Tehranipoor** West Virginia University

**Tutorials Chair** *Vita Pi-Ho Hu*National Taiwan University

**Panel Chair Tosiron Adegbija,** University of Arizona

Special Sessions Co-Chair Mimi Xie The University of Texas

at San Antonio

**Program Chair Cindy Yi** Virginia Tech

**Tutorials Co-Chair**  *Xiaolin Xun* Northeastern University

Fareena Saqib

University of North Carolina

Plenary Chair Ali A. Iranmanesh

Panel Co-Chair

Silicon Valley Polytechnic Institute

Program Co-Chair

Deliang Fan

Arizona State University

Publication Chair Paul Wesling

Hewlett Packard (retired)

Special Sessions Chair Hossein Sayadi

California State University, Long Beach

### GLOBAL REPRESENTATIVES

**Europe Chair George P. Alexiou** University of Patras and RA-CTI, Patras, Greece

**China Chair Gaofeng Wang**Hangzhou Dianzi University

Brazil & South America Chair Fabiano Passuelo Hessel Pontificia Universidade Catolica d

Pontificia Universidade Catolica do Rio do Sul, Brazil

**Japan Chair Masahiro Fujita** University of Tokyo **Taiwan Chair Shih-Hsu Huang** Chung Yuan Christian University

### **TECHNICAL PROGRAM COMMITTEES**

Cognitive Computing Hardware (CCH)

Caiwen Ding, University of Connecticut (Chair)

Zhen Zhou, Intel Corp (Co-Chair)

Committee Members: Divya Akella Kamakshi - NVIDIA Hongyu An - Michigan Technological University Kang Jun Bai - Air Force Research Laboratory Deliang Fan - Arizona State University

**Haowen Fang - Synopsys**

Xin Fu - University of Houston Miao Hu - Tetramem Inc. Doo Seok Jeong - Hanyang University Omid Kavehei - The University of Sydney Xue Lin - Northeastern University Xiaolong Ma - Clemson University Ao Ren - Chongqing University Ishan Thakkar - University of Kentucky

### **TECHNICAL PROGRAM COMMITTEES**

(continued)

### **Electronic Design Automation Tools and Methodologies (EDA)**

Srinivas Katkoori, University of South Florida (Chair) Srini Krishnamoorthy, Intel Corp. (Co-Chair)

**Committee Members:**

Abdullah Baz - UQU

Pradeep Chawda - Apple Inc

Deliang Fan - Arizona State University

Dhruva Ghai - ORIENTAL UNIVERSITY INDORE

Xinfei Guo - Shanghai Jiao Tong University

Shih-Hsu Huang - Chung Yuan Christian University

Sheikh Ariful Islam - University of Texas Rio Grande Valley

Anand Iyer - Microsoft

Yu-Min Lee - National Yang Ming Chiao Tung University

Jerome Lescot - ST Microelectronics

Rung-Bin Lin - Yuan Ze University

Bin Lin - Cadence Design Systems

Murthy Palla - Synopsys Inc.

Chidhambaranathan Rajamanikkam - Synopsys

**Andre Reis - UFRGS**

**Emre Salman - Stony Brook University**

Takashi Sato - Kyoto University

Jia Wang - Illinois Institute of Technology

Hua Xiang - IBM Research

**Georgios Zervakis - University of Patras**

**Rui Zhang - Cadence Design Systems**

### **Design Test and Verification (DTV)**

Deepashree Sengupta, Synopsys Inc. (Chair)

Chidhambaranathan Rajamanikkam, Synopsys (Co-Chair)

### Committee Members:

George Alexiou - Univ. Of PATRAS

Serge Demidenko - Sunway University

Deliang Fan - Arizona State University

Patrick Girard - LIRMM / CNRS

Chrysovalantis Kavousianos - Department of Computer Science and Engineering, University of Ioannina

**Dimitris Nikolos - University of Patras**

Ernesto Sanchez - Politecnico di Torino

**Yiorgos Tsiatouhas - University of Ioannina**

Miroslav Velev - Aries Design Automation

Arnaud Virazel - LIRMM

### System-level Design and Methodologies (SDM)

Bo Yuan, Rutgers University (Chair)

Shiyan Hu, University of Southampton (Co-Chair)

### **Committee Members:**

Deliang Fan - Arizona State University

Shrikrishna Hebbar - RV College of Engineering

**Fabiano Hessel - PUCRS**

Hana Kubatova - CTU in Prague

Xiaosen Liu - Tsinghua University

Carlos Moratelli - UFSC

Antonio Nunez - University of Las Palmas GC

Jan Schmidt - Czech Technical University in Prague

Jihee Seo - Synopsys

Vaibhav Verma - Qualcomm

Dongkuan Xu - North Carolina State University

### **TECHNICAL PROGRAM COMMITTEES**

(continued)

### Circuit Design, 3D Integration and Advanced Packaging (ICAP)

Abhronil Sengupta, The Pennsylvania State University (Chair)

Rouwaida Kanj, Synopsys/American University of Beirut(on Leave) (Co-Chair)

### **Committee Members:**

Ali Afzali-Kusha - University of Tehran Amit Agarwal - Intel Corporation

Iraklis Anagnostopoulos - Southern Illinois University Carbondale

Kirti Bhanushali - Cadence Design Systems

Karan Bhatia - Texas Instruments, Inc.

Paulo Butzen - Universidade Federal do Rio Grande Sul

Yuanqing Cheng - Beihang University

Shomit Das - Qualcomm

Vittorio Ferrari - University of Brescia

**Tobias Gemmeke - RWTH Aachen University**

Na Gong - University of South Alabama

Zhong Guan - UC Santa Barbara

Ankur Guha Roy - Broadcom Inc.

Steven Hsu - Intel Corp.

Manjunath Kareppagoudr - Advanced Micro Devices inc

Dae Hyun Kim - Washington State University

**Rakesh Kumar - Ampere Computing**

Joshua Lee - Institute of Microelectronics (A\*STAR)

Jin-Fu Li - National Central University

Rakeshkumar Mahto - California State University, Fullerton

Rashmi Mehrotra - Synopsys

Venkata Naresh Mudhireddy - Intel Corporation

Vojin Oklobdzija - University of California Davis

**Shreepad Panth - Qualcomm**

Joseph Riad - Micron Technology

Thilo Sauter - Danube University Krems

Ali Shahi - GlobalFoundries

Vishnoi Upasna - Marvell Semiconductor Inc.

Hechen Wang - Intel Labs

Cindy Yang Yi - Virginia Tech

Amir Zjajo - Innatera Nanosystems

### Special Sessions (SS)

Hossein Sayadi, California State University, Long Beach (Chair) Mimi Xie, The University of Texas at San Antonio (Co-Chair)

### **Committee Members:**

Gina Adam - The George Washington University

Yu Bai - California State University Fullerton

Jaya Dofe - California State University

Mohamed El-Hadedy - CalPoly Pomona

**Ava Hedayatipour - CSULB**

Chen Pan - Texas A&M University-Corpus Christi

**Richard Yarnell - University of Central Florida**

**Baogang Zhang - University of Central Florida**

### **WIP - Work in Progress**

Deliang Fan, Arizona State University (Chair) Cindy Yang Yi, Virginia Tech (Co-Chair)

### **Committee Members:**

Ali Iranmanesh - International Society for Quality Electronic Design Sara Tehranipoor - West Virginia University

### **TECHNICAL PROGRAM COMMITTEES**

(continued)

### **Hardware and System Security (HSS)**

Nima Karimian, West Virginia University (Chair) Anupam Chattopadhyay, Nanyang Technological University (Co-Chair)

### **Committee Members:**

Hari Cherupalli - Synopsys

**Alvaro Cintas Canto - Marymount University**

Avani Dave - Intel Corp. Inc

Chenglu Jin - CWI Amsterdam

Jan Moritz Joseph - RWTH Aachen University

**Everton Matos - Technology Innovation Institute**

Farhad Merchant - Institute for Communication Technologies and Embedded Systems, RWTH Aachen University

Seetharam Narasimhan - Nvidia Corp

**Hammond Pearce - New York University**

Francesco Regazzoni - University of Amsterdam and ALaRI - USI

Amin Rezaei - California State University, Long Beach

Soheil Salehi - Department of Electrical and Computer Engineering, University of Arizona

Hassan Salmani - Howard University

**Ioannis Savidis - Drexel University**

Hossein Sayadi - California State University, Long Beach

Zhijie Shi - University of Connecticut

Dominik Sisejkovic - Corporate Research Robert Bosch GmbH, Germany

Benjamin Tan - University of Calgary

Cindy Yang Yi - Virginia Tech

Jiliang Zhang - Hunan University

### **Emerging Device and Process Technologies and Applications (EDPT)**

Rasit Onur Topaloglu, IBM (Chair)

Lan Wei, University of Waterloo (Co-Chair)

Volkan Kursun, Norwegian University of Science and Technology (Co-Chair)

### Committee Members:

Shaahin Angizi - New Jersey Institute of Technology

Ahmedullah Aziz - University of Tennessee, Knoxville

Arijit Banerjee - Advanced Micro Devices

Rajan Beera - Pall Corporation

**Atul Bhargava - STMicroelectronics**

Vita Pi-Ho Hu - National Taiwan University

Nikos Konofaos - Aristotle University of Thessaloniki

Huamin Li - University at Buffalo

Chun-Yu Lin - National Taiwan Normal University

Mehran Mozaffari Kermani - University of South Florida

Chenyun Pan - University of Texas at Arlington

Kun Oian - GLOBALFOUNDRIES

Ujwal Radhakrishna - Texas Instruments Inc.

Arman Roohi - University of Nebraska - Lincoln

Shawana tabassum - The University of Texas at Tyler

Jinhui Wang - University of South Alabama

Mustafa Berke Yelten - Istanbul Technical University

Masoud Zabihi - Notheastern University

### **GENERAL INFORMATION**

# GENERAL INFORMATION ISQED'23

April 5-7, 2023 Seven Hills Conference Center San Francisco State University

### **AWARDS & RECOGNITIONS**

Wednesday April 5, 8:40 AM - 9:00 AM

Track A - Nob Hill Room

### **Best Paper Awards**

Recipients of the ISQED'23 Best Paper Awards will be recognized in this segment of the program. The best papers are shown in Page 2 of this document.

### Keynotes Keynote 1P.1

Wednesday, April 6, 9:00 AM - 9:35 AM

# The Weakest Link: Microelectronics Security Against Physical Attacks

Prof. Domenic Forte University of Florida

### **Keynote 2P.1**

Thursday April 6, 9:00 AM - 9:35 AM

Pushing the Energy-efficiency of Deep Learning Accelerators with Hardware-Software Co-design

> Dr. Rangharajan Venkatesan NVIDIA

# Panel Discussion Sponsored by Synopsys

Wednesday, April 5, 3:15 PM - 4:45 PM

Track A - Nob Hill Room

# Driving the Future: Exploring the Intersection of Al and Autonomous Vehicles

Two rapidly emerging technologies, Artificial Intelligence (AI) and autonomous vehicles (AV), are poised to revolutionize everyday life. Industries worldwide are investing billions of dollars to advance these transformative technologies, which have seen remarkable advancements over the past few decades. However, we have only scratched the surface of their potential impact on society. This panel will feature experts in the fields of AI and AVs who will discuss the current trends in AV, with a focus on leveraging advancements in AI to accelerate the development of AV. The panel will explore topics such as the reality of AI-driven electronic design, short-term and long-term predictions of how AI and AV will interact and their potential impact, security considerations in AI-driven AV design, practical research challenges and gaps, and potential directions for addressing these gaps.

### **Panelists:**

Yankin Tanurhan - Synopsys Ravikumar Chakaravarthy - AMD Pratik Prabhanjan Brahma - Cruiz Daryush Laqab - NVIDIA

### **Moderator:**

Pallab Chatterjee - Roadway Media

### Chairs:

Tosiron Adegbija - University of Arizona (Chair)

Fareena Saqib - University of North Carolina (Co-Chair)

### **GENERAL INFORMATION**

### **Embedded Tutorials**

### **Chair & Moderators:**

Vita Pi-Ho Hu - National Taiwan University (Chair) Xiaolin Xun - Northeastern University (Co-Chair)

### Track A - Nob Hill Room Tutorial 1

Wednesday, April 5, 12:25 PM -1:25 PM

Design Automation for Learning-Enabled Cyber-Physical Systems

Prof. Qi Zhu

Northwestern University

### **Tutorial 2**

Thursday April 6, 1:05 PM -2:05 PM

Introduction to Quantum Computing: from Algorithm to Hardware

**Prof. Hiu Yung Wong**

San Jose State University

### **TECHNICAL SESSIONS**

There are a total of 20 paper sessions held on Wednesday to Friday. Technical sessions are held in the format of three parallel tracks **A**, **B**, **C** located respectively in Nob Hill Room, Russian Hill Room, and Mt. Davidson room.

### ON-SITE REGISTRATION

Tentative time schedule of on-site registration is as follows:

Wednesday, April 5, 8:00 AM - 2:00 PM Thursday, April 6, 8:00 AM - 12:00 PM

Registration desk location will be at the conference center lobby.

### Seven Hills Conference Center

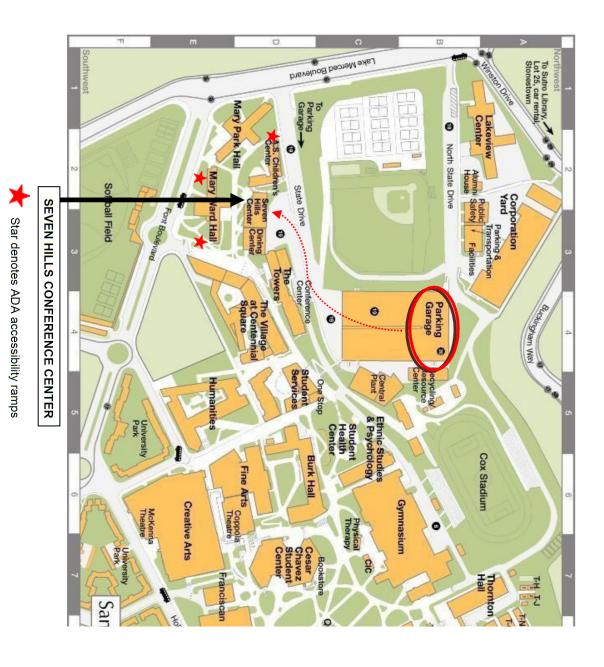

ISQED'23 conference will be held in Seven Hills Conference Center, located in San Francisco State University, 800 Font Blvd, San Francisco, CA 94132.

If you are using navigator the best address to use is: 796 state drive, San Francisco, CA 94132. (Note: make sure to use Google Maps app) At the end of State Drive is the Public Parking Lot ("Lot 20"). Parking is \$6.25 for less than 2 hours, and \$10 for 2+ hours. Pay stations on each floor accept \$1, \$5 and \$10 bills as well as credit/debit cards. Be advised, pay stations do not provide change. Please have exact amount. From the garage, Seven Hills' entrance can be accessed from State Drive by walking Southwest towards the A.S. Children's Center and taking the staircase beside it up one flight. Wheelchair access: go past the A.S. Children's Center and take a left onto the path. Follow to the entrance to the Seven Hills Conference Center.

8

### **UNIVERSITY MAP & CONFERENCE CENTER LOCATION+**

# **PROGRAM AT A GLANCE**

### **WEDNESDAY APRIL 5**

Please note all shown times are Pacific Daylight Time (PDT)

Wednesday, April 5, 2023

|       | 13:30pm-15:10pm  Advances in Circuit and  Physical Design  Recent Advances in Secure  Room)  Recent Advances in Secure  Efficiency and Relia | Break | 12:25pm-13:25em  Presenter:  Prof. Qi Zhu - Northwestern University | 11:40am-12:25pm Embedded Tutorial 1 | Systems  Design for Testability and  Verification | Session 1A (Nob Hill Room) Session 1B (Russian Hill Session 1C (Mt. D: Room)  Next Generation Computing | 10:10am=10:20am Break | 9:35am—10:10am | Keynote: 9:00am-9:35am  The Weakest Link: Microelectronics Security Against Physical Attacks  Prof. Domenic Forte - University of Florida | 8:40am-9:00am Introduction, Committee Recognitions, Best Paper Awards | Plenary Session 1: (Nob Hill Room) |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------|-------|---------------------------------------------------------------------|-------------------------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|------------------------------------|

| imory | iciency and Reliabilty of                                                                                                                    |       |                                                                     | ı                                   | Al Applications in Computing<br>System Design     | ssion 1C (Mt. Davidson<br>oom)                                                                          |                       |                | v                                                                                                                                         |                                                                       |                                    |

# **PROGRAM AT A GLANCE**

Please note all shown times are Pacific Daylight Time (PDT) Thursday, April 6, 2023

|                                                                                 |                 |                                                                                                                                                   | TH            | IURSDA                                                              | Y                                                              | APRIL 6                                                |                                                         |                                                                                                                                                                   |                                    |  |

|---------------------------------------------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--|

| 14:10pm-15:50pm                                                                 | 14:05pm-14:10pm | 13:05pm-14:05pm                                                                                                                                   | 12:25pm-13:05 | 11:45am–12:25pm                                                     | 11:40am-11:45am                                                | 10:20am–11:40am                                        | 9:35am-9:40am                                           | 8:45am–9:00am<br>9:00am–9:35am                                                                                                                                    |                                    |  |

| Session 4A (Nob Hill Room) Advances in Analysis, Simulation and Computing       |                 | Introduction to Quantum Computing: from Algorithm to Hardware <a href="Presenter:">Presenter:</a> Prof. Hiu Yung Wong - San Jose State University |               | Session 3A (Nob Hill Room) ML based CAD for Optimization            |                                                                | Session PW1 (Nob Hill Room) Poster & WIP Session 1     |                                                         | Welcome<br>Keynote:<br>Pushing the Energy-efficiency of Don. Rangharajan Venkatesan - NVIDIA                                                                      | Plenary Session 2: (Nob Hill Room) |  |

| Session 4B (Russian Hill<br>Room)<br>Hardware Security: Attacks and<br>Defenses | Break           | oom)<br>ng: from Algorithm to Hardware<br>state University                                                                                        | Lunch Break   | Session 3B (Russian Hill<br>Room)<br>Al Accelerator Hardware Design | Break                                                          | Session PW2 (Russian Hill Room) Poster & WIP Session 2 | Break                                                   | Welcome<br>Keynote:<br>Pushing the Energy-efficiency of Deep Learning Accelerators with Hardware-Software Co-design<br>Dr. Rangharajan Venkatesan - <i>NVIDIA</i> | om)                                |  |

| Session 4C (Mt. Davidson<br>Room)<br>Design for Heterogeneous<br>Integration    |                 |                                                                                                                                                   |               |                                                                     | Session3C (Mt. Davidson<br>Room)<br>Intelligent Edge Computing |                                                        | Session PW3 (Mt. Davidson Room)  Poster & WIP Session 3 |                                                                                                                                                                   | h Hardware-Software Co-design      |  |

### **FRIDAY APRIL 7**

Friday, April 7, 2023

Please note all shown times are Pacific Daylight Time (PDT)

| 10:45am–12:05pm                                                               | 10:40am-10:45am | 9:00am-10:40am                                                                                                        |  |

|-------------------------------------------------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------|--|

| Session 6A (Nob Hill Room)  Design of Emerging Circuits &  Systems            |                 | Session 5A (Nob Hill Room)<br>Low Power Circuit Design                                                                |  |

| Session 6B (Russian Hill<br>Room)<br>Novel Al Computing                       | Break           | Session 5B (Russian Hill<br>Room)<br>Advance secure circuits and<br>Hardware Trojan Detection                         |  |

| Session 6C (Mt. Davidson<br>Room)<br>Security for Resource-Limited<br>Devices |                 | Session 5C (Mt. Davidson<br>Room)<br>Efficient Algorithm, Hardware,<br>and Computing Paradigm for<br>Machine Learning |  |

### **ISQED Keynote 1P.1**

### Wednesday April 5 9:00 AM - 9:35 AM

Room: Nob Hill

# The Weakest Link: Microelectronics Security Against Physical Attacks

Prof. Domenic Forte University of Florida

For the past decade and a half, the hardware security community has expended significant time on threats related to semiconductor globalization. With the passage of the CHIPS Act in the US and similar legislation around the world, untrusted foundries should no longer be considered the weakest link. It is time to refocus efforts towards physical attacks against microelectronics. Physical attacks exist across a wide spectrum – from low-cost/low-reward non-invasive attacks to high-cost/high-reward invasive attacks – and have successfully extracted on-chip assets and broken roots-of-trust in recent years. Some non-invasive attacks have even found success remotely. Further, the threat of semi-invasive attacks, such as optical probing, is growing. Semi-invasive attacks are low in cost like non-invasive attacks but nearly as powerful as invasive attacks. This keynote will review this dangerous landscape and discuss emerging approaches that bolster physical security. It is said that "Time is what determines security. With enough time nothing is unhackable." Hence, more attention will be paid to techniques that quantifiable increase the time and complexity of physical attacks.

### **About Domenic Forte**

Domenic Forte is an Associate Professor and the Steven A. Yatauro Faculty Fellow with the Electrical and Computer Engineering Department at University of Florida. He is also Associate Director for the Florida Institute for National Security (FINS). His research covers the domain of hardware security from transistors to printed circuit boards where he has over 200 publications. Dr. Forte is a senior member of the IEEE, a member of the ACM, and serves or has served on the technical program committees of leading events such as USENIX Security, NDSS, HOST, ASHES, DAC, ICCAD, ITC, ISTFA, and BTAS. Dr. Forte is a recipient of the Presidential Early Career Award for Scientists and Engineers (PECASE), the NSF CAREER Award, and the ARO Young Investigator Award. His research has also been recognized with best paper awards and nominations from IJCB, ISTFA, HOST, DAC, and AHS. For teaching and advising, he has received the Herbert Wertheim College of Engineering Doctoral Dissertation Advisor/Mentoring Award, the Excellence in Teaching Award from UF's ECE Graduate Student Organization, and the George Corcoran Outstanding Teaching Award from University of Maryland.

### **ISQED Keynote 2P.1**

Thursday April 6 9:00 AM - 9:35 AM Room: Nob Hill

## Pushing the Energy-efficiency of Deep Learning Accelerators with Hardware-Software Co-design

Dr. Rangharajan Venkatesan *NVIDIA*

Deep neural networks (DNNs) have emerged as a key approach to solving complex problems across many application spaces, including image recognition, natural language processing, robotics, health care, and autonomous driving. Designing custom hardware accelerators for deep neural networks is highly promising, as they offer significant performance and power advantages compared to general-purpose processors. This talk presents MAGNet, a hardware-software co-design framework that explores different data formats, quantization techniques, memory hierarchies, and dataflows. This talk describes a new data format VS-Quant for achieving low-precision computation and novel multi-level dataflows to improve energy efficiency.

### **About Rangharajan Venkatesan**

Rangharajan Venkatesan is a Senior Research Scientist in the ASIC & VLSI Research group in NVIDIA. He received the B.Tech. degree in Electronics and Communication Engineering from the Indian Institute of Technology, Roorkee in 2009 and the Ph.D. degree in Electrical and Computer Engineering from Purdue University in August 2014. His research interests are in the areas of low-power VLSI design and computer architecture with a particular focus in deep learning accelerators. He has received Best Paper Awards for his work on deep learning accelerators from IEEE/ACM Symposium on Microarchitecture (MICRO) and Journal of Solid-State Circuits (JSSC). His work on spintronic memory design was recognized with the Best Paper Award at the International Symposium on Low Power Electronics and Design (ISLPED), and Best paper nomination at the Design, Automation and Test in Europe (DATE). His paper titled, "MACACO: Modeling and Analysis of Circuits for Approximate Computing", received the IEEE/ACM International Conference on Computer-Aided Design (ICCAD) Ten Year Retrospective Most Influential Paper Award in 2021. He has served as a member of the technical program committees of several leading IEEE/ACM conferences including ISSCC, DAC, MICRO, and ISLPED.

### **Panel Discussion**

Wednesday April 5 3:15 PM-4:45 PM

Room: Nob Hill

ISQED'23 panel discussion is sponsored by Synopsy

# Driving the Future: Exploring the Intersection of Al and Autonomous Vehicles

### **Summary:**

Two rapidly emerging technologies, Artificial Intelligence (AI) and autonomous vehicles (AV), are poised to revolutionize everyday life. Industries worldwide are investing billions of dollars to advance these transformative technologies, which have seen remarkable advancements over the past few decades. However, we have only scratched the surface of their potential impact on society. This panel will feature experts in the fields of AI and AV who will discuss the current trends in AV, with a focus on leveraging advancements in AI to accelerate the development of AV. The panel will explore topics such as the reality of AI-driven electronic design, short-term and long-term predictions of how AI and AV will interact and their potential impact, security considerations in AI-driven AV design, practical research challenges and gaps, and potential directions for addressing these gaps.

### **Panelists:**

Yankin Tanurhan - Synopsys Ravikumar Chakaravarthy - AMD Daryush Laqab - NVIDIA Pratik Prabhanjan Brahma - Cruise

### **Modedrator:**

Pallab Chatterjee - Roadway Media

### **Panel Committee:**

**Tosiron Adegbija -** University of Arizona (Chair) **Fareena Saqib -** University of North Carolina, Charllotte (Co-Chair)

### **Embedded Tutorial 1**

Wednesday April 5

12:25 AM - 1:25 PM

Nob Hill Room

### **Design Automation for Learning-Enabled Cyber-Physical Systems**

Prof. Qi Zhu

Northwestern University

### **Summary:**

Future learning-enabled cyber-physical systems (LE-CPSs), such as self-driving cars and robotic systems, will employ complex machine learning-based sensing, computation and communication components for their perception, prediction, planning, control, and coordination. However, ensuring their safety, robustness and security faces tremendous challenges, given the highly dynamic and uncertain environment they operate within, the fast increase of their functional and architectural complexity, the difficulty in analyzing deep neural network-based components, and the often-stringent resource and timing constraints. This calls for new design automation methodologies and tools that support rigorous, accurate and efficient modeling, synthesis, verification, and adaptation of LE-CPSs. In this tutorial, using connected and autonomous vehicles (CAVs) as an example, I will discuss these challenges and present some of our recent work to address them in a holistic manner, including 1) end-to-end verification, design and adaptation methods for ensuring robust and safe application of neural networks in perception and decision making; and 2) cross-layer methods based on weakly-hard paradigm for mitigating execution disturbances (e.g., timing violations, soft errors, malicious attacks).

### **About Qi Zhu**

Qi Zhu is an Associate Professor at the ECE Department in Northwestern University. He received a Ph.D. in EECS from University of California, Berkeley in 2008, and a B.E. in CS from Tsinghua University in 2003. His research interests include design automation for cyber-physical systems (CPS) and Internet of Things, safe and secure machine learning for CPS and IoT, cyber-physical security, and system-on-chip design, with applications in domains such as connected and autonomous vehicles, energy-efficient smart buildings, and robotic systems. He is a recipient of the NSF CAREER award, the IEEE TCCPS Early-Career Award, and the Humboldt Research Fellowship for Experienced Researchers. He received best paper awards at DAC 2006, DAC 2007, ICCPS 2013, ACM TODAES 2016, and DATE 2022. He is the Conference Chair of IEEE TCCPS, and VP of Young Professionals at IEEE CEDA. He is an Associate Editor for IEEE TCAD, ACM TCPS, and IET Cyber-Physical Systems: Theory & Applications, and has served as a Guest Editor for the Proceedings of the IEEE, ACM TCPS, IEEE T-ASE, Elsevier JSA, and Elsevier Integration, the VLSI journal.

### **Embedded Tutorial 2**

Thursday April 6

1:05 PM - 2:05 PM

Nob Hill Room

### **Introduction to Quantum Computing: from Algorithm to Hardware**

**Prof. Hiu Yung Wong**San Jose State University

### **Summary**:

Quantum computing is expected to change the world by providing exponential speed-up in solving some very difficult problems. In this tutorial, we will first discuss the fundamental principles of quantum computing algorithms. We will run one of the basic quantum algorithms, the Deutsch algorithm, on IBM's quantum computer to further appreciate the origin of speed-up and the limitations in quantum computers. Error correction, which is essential to realize a fault-tolerant quantum computer, will be briefly covered. Finally, using the superconductor-based quantum computer as an example, we will study how to implement the essential operations in quantum computers, namely, qubit initialization, readout, and manipulations. It will be appreciated that powerful classical computers, which are used to control the qubits, are essential to the successful implementation of quantum computers.

### **About Hiu Yung Wong**

Hiu Yung Wong is an Associate Professor and Silicon Valley AMDT Endowed Chair in Electrical Engineering, at San Jose State University. He received his Ph.D. degree in Electrical Engineering and Computer Science from the University of California, Berkeley in 2006. From 2006 to 2009, he worked as a Technology Integration Engineer at Spansion. From 2009 to 2018, he was a TCAD Senior Staff Application Engineer at Synopsys. He received the Curtis W. McGraw Research Award from ASEE Engineering Research Council in 2022, the NSF CA-REER award and the Newnan Brothers Award for Faculty Excellence in 2021, and Synopsys Excellence Award in 2010. He is the author of the book, "Introduction to Quantum Computing: From a Layperson to a Programmer in 30 Steps". He is one of the founding faculties of the Master of Science in Quantum Technology at San Jose State University. His research interests include the application of machine learning in simulation and manufacturing, cryogenic electronics, quantum computing, and wide bandgap device simulations. His works have produced 1 book, 1 book chapter, more than 100 papers, and 10 patents.

### **SESSION 1A**

### Wednesday April 5

### **Next Generation Computing Systems**

Chair: Arnab Raha, Intel

Co-Chair: Kang Jun Bai, AFRL

10:20AM

1A.1

A SPICE-based Framework to Emulate Quantum Circuits with classical LC Resonators

Md Mazharul Islam¹, Shafayat Hossain², Ahmedullah Aziz³

<sup>1</sup>The University of Tennessee, <sup>2</sup>Princeton University, <sup>3</sup>University of Tennessee, Knoxville

10:40AM

1A.2

Metal Inter-layer Via Keep-out-zone in M3D IC: A Critical Process-aware Design Consideration

Madhava Sarma Vemuri and Umamaheswara Tida North Dakota State University

11:00AM

1A.3

AGNI: In-Situ, Iso-Latency Stochastic-to-Binary Number Conversion for In-DRAM

94 Deep Learning

Supreeth Mysore Shivanandamurthy, Sairam Sri Vatsavai, Ishan Thakkar, sayedahmad salehi

University of Kentucky

11:20AM

1A.4

Design and Evaluation of multipliers for hardware accelerated on-chip EdDSA

Harshita Gupta<sup>1</sup>, Mayank Kabra<sup>2</sup>, Nitin Patwari<sup>3</sup>, Prashanth H C<sup>4</sup>, Madhav Rao<sup>5</sup>

<sup>1</sup>Thapar institute of information technology, Patiala, <sup>2</sup>Student, <sup>3</sup>Student, IIITB, <sup>4</sup>IIIT-Bangalore, <sup>5</sup>International Institute of Information Technology-Bangalore

### **SESSION 1B**

### Wednesday April 5

### **Design for Testability and Verification**

Chair: Chidhambaranathan R, Synopsys

10:20AM

1B.1

### 120 Self-Checking Performance Verification Methodology for Complex SoCs

Prokash Ghosh<sup>1</sup>, Aditya Chopra<sup>1</sup>, Dwaraka Pai<sup>2</sup>, Baljinder Sood<sup>2</sup>

<sup>1</sup>NXP Semiconductor Inc, USA, <sup>2</sup>NXP Semiconductors Inc, USA

10:40AM

1B.2

### 22 Polynomial Formal Verification of a Processor: A RISC-V Case Study

Lennart Weingarten<sup>1</sup>, Alireza Mahzoon<sup>1</sup>, Mehran Goli<sup>1</sup>, Rolf Drechsler<sup>2</sup>

<sup>1</sup>University of Bremen, <sup>2</sup>University of Bremen/DFKI

11:00AM

1B.3

# Application of Machine Learning for Quality Risk Factor Analysis of Electronic Assemblies

Brendan Reidy<sup>1</sup>, David Duggan<sup>1</sup>, Bernard Glasauer<sup>2</sup>, Peng Su<sup>2</sup>, Ramtin Zand<sup>1</sup>

<sup>1</sup>University of South Carolina, <sup>2</sup>Component Engineering, Juniper Networks

11:20AM

1B.4

### 70 Quality-driven Design Methodology for PUFs in FPGAs for Secure IoT

Xiangyun Wang<sup>1</sup>, Yicheng Song<sup>1</sup>, Katyayani Prakash<sup>1</sup>, Zeljko Zilic<sup>1</sup>, Tomas Langsetmo<sup>2</sup>

<sup>1</sup>McGill University, <sup>2</sup>KNOX Industries Inc.

### **SESSION 1C**

### Wednesday April 5

### **AI Applications in Computing System Design**

Chair: Hossein Sayadi, California State University, Long Beach

10:20AM

1C.1

HD2FPGA: Automated Framework for Accelerating Hyperdimensional Computing

174 on FPGAs

Tianqi Zhang<sup>1</sup>, Sahand Salamat<sup>2</sup>, Behnam Khaleghi<sup>2</sup>, Justin Morris<sup>3</sup>, Baris Aksanli<sup>4</sup>, Tajana Rosing<sup>1</sup>

<sup>1</sup>UCSD, <sup>2</sup>University of California, San Diego, <sup>3</sup>CSUSM, <sup>4</sup>San Diego State University

10:40AM

1C.2

XOR-CiM: An Efficient Computing-in-SOT-MRAM Design for Binary Neural Network

114 Acceleration

Mehrdad Morsali<sup>1</sup>, Ranyang Zhou<sup>1</sup>, Sepehr Tabrizchi<sup>2</sup>, Arman Roohi<sup>3</sup>, Shaahin Angizi<sup>1</sup> New jersey Institute of Technology, <sup>2</sup>University of Nebraska–Lincoln, <sup>3</sup>University of Nebraska - Lincoln

11:00AM

1C.3

117 Security and Reliability Challenges in Machine Learning for EDA: Latest Advances

Zhiyao Xie, Tao Zhang, Yifeng Peng

Hong Kong University of Science and Technology

11:20AM

1C.4

187 Image-Based Zero-Day Malware Detection in IoMT Devices: A Hybrid Al-Enabled

Method

Zhangying He and Hossein Sayadi California State University, Long Beach

### **SESSION 2A**

### Wednesday April 5

### **Advances in Circuit and Physical Design**

Chair: Rui Zhang, Cadence Inc.

Co-Chair: Sheikh Ariful Islam, University of Texas Rio Grande Valley

1:30PM

2A.1

### 101 Routability-aware Placement Guidance Generation for Mixed-size Designs

Chieh-Yu Cheng and Ting-Chi Wang National Tsing Hua University

1:50PM

2A.2

### 103 MC-MCF: A Multi-Capacity Model for Ordered Escape Routing

Zhenyi Gao, Sheqin Dong, Zhicong Tang, Wenjian Yu Tsinghua University

2:10PM

2A.3

### DC-Model: A New Method for Assisting the Analog Circuit Optimization

Yuan Wang, Jian Xin, Haixu Liu, Qian Qin, Chenkai Chai, Yukai Lu, Jinglei Hao, Jianhao Xiao, Zuochang Ye, Yan Wang Tsinghua University

2:30PM

2A.4

# Accounting for Floorplan Irregularity and Configuration Dependence in FPGA Routing Delay Models

Gabriel Barajas<sup>1</sup>, Jonathan Greene<sup>2</sup>, Fei Li<sup>1</sup>, James Tandon<sup>3</sup>

<sup>1</sup>Microchip, <sup>2</sup>Cambios Computing LLC, <sup>3</sup>California State University East Bay

2:50PM

2A.5

### 171 An Effective Cost-Skew Tradeoff Heuristic for VLSI Global Routing

Andrew Kahng<sup>1</sup>, Shreyas Thumathy<sup>2</sup>, Mingyu Woo<sup>3</sup>

<sup>1</sup>UCSD CSE and ECE Departments, <sup>2</sup>Canyon Crest Academy, <sup>3</sup>UCSD ECE Department

### **SESSION 2B**

### Wednesday April 5

### **Recent Advances in Secure Hardware Design**

Chair: Soheil Salehi, University of Arizona

1:30PM

2B.1

### **Automated Supervised Topic Modeling Framework for Hardware Weaknesses**

Rakibul Hassan¹, Charan Bandi¹, Meng-Tien Tsai², Shahriar Golchin³, Sai Manoj Pudukotai Dinakarrao¹, Setareh Rafatirad², Soheil Salehi⁴

¹George Mason University, ²University of California Davis, ³University of Arizona, ⁴Department of Electrical and Computer Engineering, University of Arizona

1:50PM

2B.2

### 19 Polymorphic Sensor to Detect Laser Logic State Imaging Attack

Sourav Roy<sup>1</sup>, Shahin Tajik<sup>2</sup>, Domenic Forte<sup>1</sup>

<sup>1</sup>University of Florida, <sup>2</sup>Worcester Polytechnic Institute

2:10PM

2B.3

### 122 Low Overhead System-Level Obfuscation through Hardware Resource Sharing

Daniel Xing<sup>1</sup>, Michael Zuzak<sup>2</sup>, Ankur Srivastava<sup>1</sup>

<sup>1</sup>University of Maryland, <sup>2</sup>Rochester Institute of Technology

2:30PM

2B.4

### 79 SPRED: Spatially Distributed Laser Fault Injection Resilient Design

tasnuva farheen<sup>1</sup>, Shahin Tajik<sup>2</sup>, Domenic Forte<sup>1</sup>

<sup>1</sup>University of Florida, <sup>2</sup>Worcester Polytechnic Institute

2:50PM

2B.5

98 Enlarging Reliable Pairs via Inter-Distance Offset for a PUF Entropy-Boosting Algorithm

Md Omar Faruque and Wenjie Che New Mexico State University

### **SESSION 2C**

### Wednesday April 5

### **Efficiency and Reliability of Memory**

Chair: Hongyu An, Michigan Technological University

1:30PM

2C.1

# 49 eDRAM-OESP: A novel performance efficient in-embedded-DRAM-compute design for on-edge signal processing application

Mayank Kabra<sup>1</sup>, Prashanth H C<sup>2</sup>, Kedar Deshpande<sup>1</sup>, Madhav Rao<sup>3</sup>

<sup>1</sup>Student, <sup>2</sup>IIIT-Bangalore, <sup>3</sup>International Institute of Information Technology-Bangalore

1:50PM

2C.2

CMDS: Cross-layer Dataflow Optimization for DNN Accelerators Exploiting Multi-

### 115 bank Memories

$\label{eq:man_shi_loss} \textit{Man Shi}^1, \textit{Steven Colleman}^1, \textit{Charlotte VanDeMieroop}^1, \textit{Antony Joseph}^2, \textit{Maurice Meijer}^2, \textit{Wim Dehaene}^1, \textit{Marian Verhelst}^1$

<sup>1</sup>KU Leuven, <sup>2</sup>NXP Semiconductor

2:10PM

2C.3

HIE-DRAM: High-Performance Efficient In-DRAM Computing Architecture for SIMD

${\it Mayank~Kabra}^{1}, {\it Prashanth~H~C^{2}}, {\it Kedar~Deshpande}^{1}, {\it Madhav~Rao}^{3}$

<sup>1</sup>Student, <sup>2</sup>IIIT-Bangalore, <sup>3</sup>International Institute of Information Technology-Bangalore

2:30PM

2C.4

168 AGRAS: Aging and memory request rate aware scheduler for PCM memories

Aswathy NS<sup>1</sup> and Hemangee Kapoor<sup>2</sup>

<sup>1</sup>IIT Guwahati, <sup>2</sup>Indian Institute of Technology Guwahati

### **SESSION PW1**

### **Thursday April 6**

### PW1

Chair: Hossein Sayadi, California State University, Long Beach

9:40AM

PW1.1

Accurate Estimation of Circuit Delay Variance with Limited Monte Carlo Simulations

Using Bayesian Inference

Chithira R.

National Institute of Technology Calicut

9:45AM

PW1.2

DSEAdd: FPGA based Design Space Exploration for Approximate Adders with Variable Bit-precision

Archie Mishra and Nanditha Rao

**IIIT Bangalore**

9:50AM

### PW1.3

# **Emerging Interconnect Exploration for SRAM Application Using Nonconventional H- Tree and Center-Pin Access**

Zhenlin Pei¹, Mahta Mayahinia², Hsiao-Hsuan Liu³, Mehdi Tahoori², Shairfe Salahuddin⁴, Francky Catthoor⁴, Zsolt Tokei⁴, Chenyun Pan⁵

¹The University of Texas at Arlington, ²Karlsruhe institute of technology (KIT), ³Katholieke Universiteit Leuven (KU Leuven), ⁴IMEC, ⁵University of Texas at Arlington

9:55AM

PW1.4

### A Low-overhead PUF-based Secure Scan Design

Wei Zhou<sup>1</sup>, Aijiao Cui<sup>1</sup>, Cassi Chen<sup>2</sup>, Gang Qu<sup>3</sup>

<sup>1</sup>Harbin Institute of Technology (Shenzhen), <sup>2</sup>University of California, Berkeley, <sup>3</sup>University of Maryland

10:00AM

PW1.5

31 Deep Image Segmentation for Defect Detection in Photo-lithography Fabrication Omari Paul<sup>1</sup>, Sakib Abrar<sup>1</sup>, Richard Mu<sup>1</sup>, Riadul Islam<sup>2</sup>, Manar Samad<sup>1</sup> <sup>1</sup>Tennessee State University, <sup>2</sup>University of Maryland at Baltimore County

10:05AM

PW1.6

36 Performance Analysis of Cylindrical Through Silicon Via with Interfacial Crack

Vandana Kumari, Maya Chandrakar, Manoj Majumder

IIIT Naya Raipur

10:10AM

PW1.7

# A Flexible Cluster Tool Simulation Framework with Wafer Batch Dispatching Time Recommendation

Hsin-Ping Yen<sup>1</sup>, Shiuan-Hau Huang<sup>1</sup>, Yan-Hsiu Liu<sup>2</sup>, Kuang-Hsien Tseng<sup>2</sup>, Ji-Fu Kung<sup>2</sup>, Yi-Ting Li<sup>1</sup>, Yung-Chih Chen<sup>3</sup>, Chun-Yao Wang<sup>4</sup>

<sup>1</sup>National Tsing Hua University, <sup>2</sup>United Microelectronics Corporation, <sup>3</sup>National Taiwan University of Science and Technology, <sup>4</sup>Dept. CS, National Tsing Hua University

10:15AM

### PW1.8

# Hardware Performance Counter Enhanced Watchdog for Embedded Software Security

Karl Ott<sup>1</sup> and Rabi N. Mahapatra<sup>2</sup>

<sup>1</sup>Texas A&M University, <sup>2</sup>Professor

10:20AM

PW1.9

### 60 Power Savings in USB Hubs Through a Proactive Scheduling Strategy

Bikrant Das Sharma<sup>1</sup>, Abdul Ismail<sup>2</sup>, Chris Meyers<sup>3</sup>

<sup>1</sup>Rice University, <sup>2</sup>Intel Corporation, USB Implementers Forum, <sup>3</sup>Fresco Logic

10:25AM

PW1.10

### 63 DK Lock: Dual Key Logic Locking Against Oracle-Guided Attacks

Jordan Maynard<sup>1</sup> and Amin Rezaei<sup>2</sup>

<sup>1</sup>California State University Long Beach, <sup>2</sup>California State University, Long Beach

### **SESSION PW2**

### **Thursday April 6**

### PW2

Chair: Kang Jun Bai, AFRL

9:40AM

PW2.1

Reproducing Fear Conditioning of Rats with Unmanned Ground Vehicles and Neuromorphic Systems

Noah Zins and Hongyu An

Michigan Technological University

9:45AM

PW2.2

71 High-Throughput Hardware Implementation for Haraka in SPHINCS+

Yueqin Dai, Yifeng Song, Jing Tian, Zhongfeng Wang Nanjing University

9:50AM

PW2.3

Analysis of Machine Learning Techniques for Time Domain Waveform Prediction in Analog and Mixed Signal Integrated Circuit Verification

74 Dhanasekar V¹, Vinodhini Gunasekaran¹, Anusha Challa¹, Bama Srinivasan¹, Dhurga Devi J¹, Selvi Ravindran¹, Ranjani Parthasarathi¹, Ramakrishna P V¹, Gopika Geetha Kumar², Venkateswaran Padmanabhan³, Guha Lakshmanan³, Lakshmanan Balasubramanian³

<sup>1</sup>College of Engineering Guindy, Anna University, <sup>2</sup>Carnegie Mellon University, Pennsylvania, <sup>3</sup>Texas Instruments (India) Pvt. Ltd.

9:55AM

PW2.4

### Focusing on the Key Suspicious Trojan Nets with a Collaborative Approach

75 Shih-Lung Pao<sup>1</sup>, Chuan-Pin Huang<sup>1</sup>, Yen-Chi Peng<sup>1</sup>, Ing-Jer Huang<sup>2</sup>

<sup>1</sup>Department of Computer Science and Engineering, National Sun Yat-Sen

University, <sup>2</sup>Department of Computer Science and Engineering, Digital Content and

Multimedia Technology Research Center, National Sun Yat-Sen University

10:00AM

PW2.5

### CMP-SiL: Confidential Multi Party Software-in-the-Loop Simulation Framework

134 Shalabh Jain<sup>1</sup>, Pradeep Pappachan<sup>1</sup>, Jorge Guajardo<sup>2</sup>, Sven Trieflinger<sup>3</sup>, Indrasen Raghupatruni<sup>3</sup>, Thomas Huber<sup>3</sup>

<sup>1</sup>Robert Bosch LLC, <sup>2</sup>Bosch Research and Technology Center, Robert Bosch LLC, <sup>3</sup>Robert Bosch GmbH

10:05AM

PW2.6

A2OP: an A\* Algorithm OPtimizer with the Heuristic Function for PCB Automatic Routing

Quanbao Guo and Keni Qiu Capital Normal University

10:15AM

PW2.7

Decomposable Architecture and Fault Mitigation Methodology for Deep Learning

82 Accelerators

Ning-Chi Huang<sup>1</sup>, Min-Syue Yang<sup>1</sup>, Ya-Chu Chang<sup>1</sup>, Kai-Chiang Wu<sup>2</sup>

<sup>1</sup>Department of Computer Science, National Yang Ming Chiao Tung

University, <sup>2</sup>Department of Computer Science, National Chiao Tung University

10:20AM

PW2.8

97 NetViz: A Tool for Netlist Security Visualization

James Geist<sup>1</sup>, Travis Meade<sup>1</sup>, Shaojie Zhang<sup>1</sup>, Yier Jin<sup>2</sup>

<sup>1</sup>University of Central Florida, <sup>2</sup>University of Florida

10:25AM

### PW2.9

102

# A True Random Number Generator for Probabilistic Computing using Stochastic Magnetic Actuated Random Transducer Devices

Ankit Shukla<sup>1</sup>, Laura Heller<sup>1</sup>, Md Golam Morshed<sup>2</sup>, Laura Rehm<sup>3</sup>, Avik Ghosh<sup>2</sup>, Andrew Kent<sup>3</sup>, Shaloo Rakheja<sup>1</sup>

<sup>1</sup>University of Illinois at Urbana-Champaign, <sup>2</sup>University of Virginia, <sup>3</sup>New York University

10:30AM

PW2.10

# Attributed Graph Transformation for Generating Synthetic Benchmarks for Hardware Security

Juneeth kumar Meka and Ranga Vemuri University of Cincinnati

### **SESSION PW3**

### **Thursday April 6**

### PW3

Chair: Vidya Chhabria, Arizona State University

9:40AM

PW3.1

# Secure Control Loop Execution of Cyber-Physical Devices Using Predictive State Space Checks

Kwondo Ma<sup>1</sup>, Chandramouli Amarnath<sup>1</sup>, Abhijit Chatterjee<sup>1</sup>, Jacob Abraham<sup>2</sup>

<sup>1</sup>Georgia Institute of Technology, <sup>2</sup>University of Texas at Austin

9:45AM

PW3.2

### Cryogenic In-memory Binary Multiplier Using Quantum Anomalous Hall Effect

### 131 Memories

Arun Govindankutty<sup>1</sup>, Shamiul Alam<sup>2</sup>, Sanjay Das<sup>1</sup>, Ahmedullah Aziz<sup>2</sup>, Sumitha George<sup>1</sup>

<sup>1</sup>North Dakota State University, <sup>2</sup>The University of Tennessee, Knoxville

9:50AM

PW3.3

### 140 SQRTLIB: Library of Hardware Square Root Designs

Prashanth H C<sup>1</sup>, Sriniketh S S<sup>2</sup>, Shrikrishna Hebbar<sup>2</sup>, Chinmaye R<sup>2</sup>, Madhav Rao<sup>3</sup>

<sup>1</sup>IIIT-Bangalore, <sup>2</sup>RVCE, <sup>3</sup>International Institute of Information Technology-Bangalore

9:55AM

PW3.4

# Binary Synaptic Array for Inference and Training with Built-in RRAM Electroforming Circuit

Ashvinikumar Dongre and Gaurav Trivedi Indian Institute of Technology Guwahati India 10:00AM

PW3.5

### 149 Neural Network Partitioning for Fast Distributed Inference

Robert Viramontes and Azadeh Davoodi University of Wisconsin - Madison

10:05AM

PW3.6

# DAGGER: Exploiting Language Semantics for Program Security in Embedded Systems

Garett Cunningham, Harsha Chenji, Gordon Stewart, David Juedes, Avinash Karanth Ohio University

10:10AM

PW3.7

# Exploiting Programmable Dipole Interaction in Straintronic Nanomagnet Chains for Ising Problems

Nastaran Darabi<sup>1</sup>, Maeesha Binte Hashem<sup>1</sup>, Supriyo Bandyopadhyay<sup>2</sup>, Amit Trivedi<sup>1</sup> <sup>1</sup>University of Illinois at Chicago, <sup>2</sup>Virginia Commonwealth University

10:15AM

PW3.8

### 157 A Bit-Parallel Deterministic Stochastic Multiplier

Sairam Sri Vatsavai and Ishan Thakkar University of Kentucky

10:20AM

PW3.9

### ACPC: Covert Channel Attack on Last Level Cache using Dynamic Cache Partitioning Jaspinder Kaur<sup>1</sup> and Shirshendu Das<sup>2</sup>

<sup>1</sup>Indian Institute of Technology Ropar, <sup>2</sup>Indian Institute of Technology Hyderabad

10:25AM

PW3.10

# 169 Intrinsic Parameter Fluctuation and Process Variation Effect of Vertically Stacked Silicon Nanosheet Complementary Field-Effect Transistors

Sekhar Kola, Yiming Li, Min-Hui Chuang National Yang Ming Chiao Tung University 10:30AM

PW3.11

**SpotOn: A Gradient-based Targeted Data Poisoning Attack on Deep Neural**

### 176 Networks

Yash Khare<sup>1</sup>, Kumud Lakara<sup>2</sup>, Sparsh Mittal<sup>3</sup>, Arvind Kaushik<sup>4</sup>, Rekha Singhal<sup>5</sup>

<sup>1</sup>Amrita Vishwa Vidyapeetham, <sup>2</sup>Manipal Institute of Technology, <sup>3</sup>IIT Roorkee, <sup>4</sup>NXP Semiconductors, <sup>5</sup>TCS Research

### **SESSION 3A**

### **Thursday April 6**

### **ML based CAD for Optimization**

Chair: **Murthy Palla**, Synopsys Inc. Co-Chair: **Rui Zhang**, Cadence Inc.

10:45AM

3A.1

PreAxC: Error Distribution Prediction for Approximate Computing Quality Control using Graph Neural Networks

Lakshmi Sathidevi<sup>1</sup>, Abhinav Sharma<sup>2</sup>, Nan Wu<sup>3</sup>, Xun Jiao<sup>4</sup>, Cong "Callie" Hao<sup>1</sup> <sup>1</sup>Georgia Institute of Technology, <sup>2</sup>Indian Institute of Information Technology, Guwahati, <sup>3</sup>UC Santa Barbara, <sup>4</sup>Villanova University

11:05AM

3A.2

DeepAxe: A Framework for Exploration of Approximation and Reliability Trade-offs in DNN Accelerators

86 Mahdi Taheri¹, Mohamad Riazati², Mohammad Hasan Ahmadilivani³, Maksim Jenihhin³, Masoud Daneshtalab², Jaan Raik⁴, Mikael Sjödin², Björn Lisper²

¹PhD researcher at Tallinn university of Technology, ²Mälardalen University, Västerås, ³Tallinn University of Technology, Tallinn, Estonia, ⁴Tallinn University of Technology, Tallinn

11:25AM

3A.3

121 TOTAL: Topology Optimization of Operational Amplifier via Reinforcement Learning

Zihao Chen, Songlei Meng, Fan Yang, Li Shang, Xuan Zeng Fudan University 11:45AM

3A.4

### 154 Design of Hardware Accelerators to Compute Parametric Capacitance Tables

Sandeep Koranne

**Mentor Graphics Corporation**

12:05PM

3A.5

### Dilated Involutional Pyramid Network (DInPNet): A Novel Model for Printed Circuit

### 175 Board (PCB) Components Classification

Ananya Mantravadi¹, Dhruv Makwana², Sai Chandra Teja R², Sparsh Mittal³, Rekha Singhal⁴

<sup>1</sup>IIIT Raichur, <sup>2</sup>Independent Researcher, <sup>3</sup>IIT Roorkee, <sup>4</sup>TCS Research

### **SESSION 3B**

#### **Thursday April 6**

### **AI Accelerator Hardware Design**

Chair: **Kang Jun Bai**, AFRL Co-Chair: **Ji Li**, MicroSoft

10:45AM

3B.1

# An Optical XNOR-Bitcount Based Accelerator for Efficient Inference of Binary Neural Networks

Sairam Sri Vatsavai, Venkata Sai Praneeth Karempudi, Ishan Thakkar University of Kentucky

11:05AM

3B.2

### Heterogeneous Multi-Functional Look-Up-Table-based Processing-in-Memory

#### 160 Architecture for Deep Learning Acceleration

Sathwika Bavikadi<sup>1</sup>, Purab Ranjan Sutradhar<sup>2</sup>, Amlan Ganguly<sup>2</sup>, Sai Manoj Pudukotai Dinakarrao<sup>1</sup>

<sup>1</sup>George Mason University, <sup>2</sup>Rochester Institute of Technology

11:25AM

3B.3

# **HFGCN: High-speed and Fully-optimized GCN Accelerator**

MinSeok Han<sup>1</sup>, Jiwan Kim<sup>1</sup>, Donggeon Kim<sup>1</sup>, Hyunuk Jeong<sup>1</sup>, Gilho Jung<sup>1</sup>, Myeongwon Oh<sup>1</sup>, Hyundong Lee<sup>2</sup>, Yunjeong Go<sup>2</sup>, HyunWoo Kim<sup>1</sup>, Jongbeom Kim<sup>1</sup>, Taigon Song<sup>1</sup>

<sup>1</sup>Kyungpook National University (KNU), <sup>2</sup>Kyungpook National University

11:45AM

3B.4

# 90 Knowledge Distillation between DNN and SNN for Intelligent Sensing Systems on Loihi Chip

Shiya Liu<sup>1</sup> and Yang Yi<sup>2</sup>

<sup>1</sup>EMD Electronics, <sup>2</sup>Virginia Tech

12:05PM

3B.5

Lightweight Instruction Set for Flexible Dilated Convolutions and Mixed-Precision

#### 142 Operands

Simon Friedrich<sup>1</sup>, Shambhavi Balamuthu Sampath<sup>2</sup>, Robert Wittig<sup>1</sup>, Manoj Rohit Vemparala<sup>3</sup>, Nael Fasfous<sup>3</sup>, Emil Matus<sup>4</sup>, Walter Stechele<sup>5</sup>, Gerhard Fettweis<sup>1</sup>

<sup>1</sup>TU Dresden, <sup>2</sup>BMW, <sup>3</sup>BMW AG, <sup>4</sup>Technische Universität Dresden, <sup>5</sup>TUM

# **SESSION 3C**

#### **Thursday April 6**

# **Intelligent Edge Computing**

Chair: Hossein Sayadi, California State University, Long Beach

10:45AM

3C.1

PriML: An Electro-Optical Accelerator for Private Machine Learning on Encrypted Data

Mengxin Zheng<sup>1</sup>, Fan Chen<sup>1</sup>, Lei Jiang<sup>1</sup>, Qian Lou<sup>2</sup>

<sup>1</sup>Indiana University Bloomington, <sup>2</sup>University of Central Florida

11:05AM

3C.2

ISSAC: An Self-organizing and Self-healing MAC Design for Intermittent

191 Communication Systems

Ruben Dominguez<sup>1</sup>, Wen Zhang<sup>1</sup>, Hongzhi Xu<sup>2</sup>, Pablo Rangel<sup>3</sup>, Chen Pan<sup>4</sup>

<sup>1</sup>Texas A&M University - Corpus Christi, <sup>2</sup>Jishou University, <sup>3</sup>Texas A&M University - Corpus Christi, <sup>4</sup>Texas A&M University-Corpus Christi

11:25AM

3C.3

#### A Deep Learning Approach for Ventricular Arrhythmias Classification using

#### 188 Microcontroller

Ya-sine Agrignan<sup>1</sup>, Shanglin Zhou<sup>1</sup>, Jun Bai<sup>1</sup>, Sahidul Islam<sup>2</sup>, Sheida Nabavi<sup>1</sup>, Mimi Xie<sup>2</sup>, Caiwen Ding<sup>1</sup>

<sup>1</sup>University of Connecticut, <sup>2</sup>University of Texas at San Antonio

11:45AM

3C.4

### 189 Reinforcement Learning-Based Guidance of Autonomous Vehicles

Joseph Clemmons and Yufang Jin University of Texas at San Antonio

# **SESSION 4A**

### **Thursday April 6**

# **Advances in Analysis, Simulation and Computing**

Chair: **Chidhambaranathan Rajamanikkam**, Utah State University Co-Chair: **Anand Iyer**, Synopsys Inc.

2:10PM

4A.1

#### 24 Fast Electromigration Simulation for Chip Power Grids

Bijan Shahriari and Farid Najm University of Toronto

2:30PM

4A.2

#### 93 On-Interposer Decoupling Capacitors Placement for Interposer-based 3DIC

Po-Yang Chen, Chang-Yun Liu, Hung-Ming Chen, Po-Tsang Huang National Yang Ming Chiao Tung University

2:50PM

4A.3

#### 96 Analysis of Pattern-dependent Rapid Thermal Annealing Effects on SRAM Design

Vidya Chhabria<sup>1</sup> and Sachin S. Sapatnekar<sup>2</sup>

<sup>1</sup>Arizona State University, <sup>2</sup>University of Minnesota

3:10PM

4A.4

# Reverse Engineering Word-Level Models from Look-Up Table Netlists

Ram Venkat Narayanan, Aparajithan Nathamuni-Venkatesan, Kishore Pula, Sundarakumar Muthukumaran, Ranga Vemuri University of Cincinnati

3:30PM

4A.5

Novel Implementation of High-Performance Polynomial Multiplication for Unified KEM Saber based on TMVP Design Strategy

Pengzhou He and Jiafeng Xie Villanova University

# **SESSION 4B**

#### **Thursday April 6**

# **Hardware Security: Attacks and Defenses**

Chair: Soheil Salehi, University of Arizona

2:10PM

4B.1

#### Unraveling Latch Locking Using Machine Learning, Boolean Analysis, and ILP

39 Dake Chen<sup>1</sup>, Xuan Zhou<sup>1</sup>, Yinghua Hu<sup>1</sup>, Yuke Zhang<sup>1</sup>, Kaixin Yang<sup>1</sup>, Andrew Rittenbach<sup>2</sup>, Pierluigi Nuzzo<sup>1</sup>, Peter Beerel<sup>3</sup>

<sup>1</sup>University of Southern California, <sup>2</sup>USC Information Sciences Institute, <sup>3</sup>Univ. of Southern California

2:30PM

4B.2

#### **Resynthesis-based Attacks Against Logic Locking**

141 Felipe Almeida<sup>1</sup>, Levent Aksoy<sup>1</sup>, Quang-Linh Nguyen<sup>2</sup>, Sophie Dupuis<sup>2</sup>, Marie-Lise Flottes<sup>3</sup>, Samuel Pagliarini<sup>4</sup>

<sup>1</sup>Tallinn University of Technology, <sup>2</sup>LIRMM, <sup>3</sup>LIRMM CNRS, <sup>4</sup>Tallinn University of Technology (TalTech)

2:50PM

4B.3

# VAST: Validation of VP-based Heterogeneous Systems against Availability Security

167 Properties using Static Information Flow Tracking

Ece Demirhan Coskun<sup>1</sup>, Muhammad Hassan<sup>1</sup>, Mehran Goli<sup>2</sup>, Rolf Drechsler<sup>2</sup>

<sup>1</sup>Cyber-Physical Systems, DFKI GmbH, <sup>2</sup>Institute of Computer Science, University of Bremen

3:10PM

4B.4

#### 41 MAAS: Hiding Trojans in Approximate Circuits

*Qazi Arbab Ahmed*<sup>1</sup>, *Muhammad Awais*<sup>1</sup>, *Marco Platzner*<sup>2</sup>

<sup>1</sup>Paderborn University, <sup>2</sup>Paderborn University

3:30PM

4B.5

#### 106 Efficient Decryption Architecture for Classic McEliece

Xinyuan Qiao, Suwen Song, Jing Tian, Zhongfeng Wang Nanjing University

# **SESSION 4C**

# **Thursday April 6**

# **Design for Heterogeneous Integration**

Chair: Gina Adam, George Washington University

2:10PM

4C.1

Testbench on a Chip: A Yield Test Vehicle for Resistive Memory Devices

Luke Upton<sup>1</sup>, Guenole Lallement<sup>1</sup>, Michael Scott<sup>1</sup>, Joyce Taylor<sup>2</sup>, Robert

Radway<sup>1</sup>, Dennis Rich<sup>1</sup>, Mark Nelson<sup>3</sup>, Subhasish Mitra<sup>1</sup>, Boris Murmann<sup>1</sup>

Stanford University, <sup>2</sup>Intrinsix Corporation, <sup>3</sup>SkyWater Technology

2:30PM

4C.2

183 Integrating emerging devices with CMOS for analog in-memory computing Qiangfei Xia University of Massachusetts Amherst

2:50PM

4C.3

184 Integrating Emerging Memories for Analog DNN Accelerators

An Chen

**IBM**

3:10PM

4C.4

An Infrastucture for Large-scale Reconfigurable Neuronal Network Emulations

Gopabandhu Hota and Gert Cauwenberghs

UC San Diego

# **SESSION 5A**

### Friday April 7

### **Low Power Circuit Design**

Chair: **Amit Trivedi**, University of Illinois at Chicago Co-Chair: **Hongvu An**, Michigan Technological University

9:00AM

5A.1

### 173 A Novel Pseudo-Flash Based Digital Low Dropout (LDO) Voltage Regulator

Cheng-Yen Lee<sup>1</sup>, Sunil Khatri<sup>1</sup>, Sarma Vrudhula<sup>2</sup>

<sup>1</sup>Texas A&M University, <sup>2</sup>Arizona State University

9:20AM

5A.2

#### 20 A Low Power SRAM with Fully Dynamic Leakage Suppression for IoT Nodes

Jun Yin and Mircea Stan University of Virginia

9:40AM

5A.3

### Error Diluted Approximate Multipliers Using Positive And Negative Compressors

Bindu G Gowda<sup>1</sup>, Prashanth H C<sup>2</sup>, Madhav Rao<sup>3</sup>

<sup>1</sup>International Institute of Information Technology Bangalore, <sup>2</sup>IIIT-Bangalore, <sup>3</sup>International Institute of Information Technology-Bangalore

10:00AM

5A.4

#### 138 Scalable Low-Cost Sorting Network with Weighted Bit-Streams

Brady Prince<sup>1</sup>, Hassan Najafi<sup>2</sup>, Bingzhe Li<sup>1</sup>

<sup>1</sup>Oklahoma State University, <sup>2</sup>University of Louisiana

# **SESSION 5B**

#### Friday April 7

### **Advance Secure Circuits and Hardware Trojan Detection**

Chair: Setareh Rafatirad, University of California Davis

9:00AM

5B.1

# Novel, Configurable Approximate Floating-point Multipliers for Error-Resilient Applications

Vishesh Mishra<sup>1</sup>, Sparsh Mittal<sup>2</sup>, Rekha Singhal<sup>3</sup>, Manoj Nambiar<sup>3</sup>

<sup>1</sup>IIT Kanpur, <sup>2</sup>IIT Roorkee, <sup>3</sup>TCS Research

9:20AM

5B.2

#### **Design Space Exploration of Modular Multipliers for ASIC FHE accelerators**

161 Deepraj Soni¹, Mohammed Nabeel Thari Moopan², Homer Gamil³, Oleg Mazonka⁴, Brandon Reagen⁵, Ramesh Karri⁶, Michail Maniatakos⁴

¹New York University Tandon School of Engineering, ²New York University, ³NYUAD, ⁴New York University Abu Dhabi, ⁵NYU/Facebook, ⁶NYU

9:40AM

5B.3

# H-Saber: An FPGA-Optimized Version for Designing Fast and Efficient Post-Quantum Cryptography Hardware Accelerators

Andrea Guerrieri<sup>1</sup>, Gabriel Da Silva Marques<sup>2</sup>, Francesco Regazzoni<sup>3</sup>, Andres Upegui<sup>2</sup>

<sup>1</sup>EPFL and HES-SO, <sup>2</sup>University of Applied Sciences Western Switzerland, <sup>3</sup>University of Amsterdam and Universita della Svizzera Italiana

10:00AM

5B.4

#### 126 A Novel Method Against Hardware Trojans in Approximate Circuits

Yuqin Dou<sup>1</sup>, CHONGYAN GU<sup>2</sup>, Chenghua Wang<sup>1</sup>, Weiqiang Liu<sup>1</sup>

<sup>1</sup>Nanjing University of Aeronautics and Astronautics, <sup>2</sup>Queen's University Belfast

10:20AM

5B.5

# Using Path Features for Hardware Trojan Detection Based on Machine Learning

# 78 **Techniques**

Chia-Heng Yen<sup>1</sup>, Jung-Che Tsai<sup>1</sup>, Kai-Chiang Wu<sup>2</sup>

<sup>1</sup>National Yang Ming Chiao Tung University, <sup>2</sup>Department of Computer Science,

National Chiao Tung University

### **SESSION 5C**

#### Friday April 7

# Efficient Algorithm, Hardware, and Computing Paradigm for Machine Learning

Chair: Kang Jun Bai, AFRL

9:00AM

5C.1

Locality-sensing Fast Neural Network (LFNN): An Efficient Neural Network

Acceleration Framework via Locality Sensing for Real-time Videos Queries

Xiaotian Ma, Jiaqi Tang, Yu Bai

California State University, Fullerton

9:20AM

5C.2

113 Image Quantization Tradeoffs in a YOLO-based FPGA Accelerator Framework Richard Yarnell, Mousam Hossain, Ronald DeMara University of Central Florida

9:40AM

5C.3

**Automatic Subnetwork Search Through Dynamic Differentiable Neuron Pruning**

Zigeng Wang<sup>1</sup>, Bingbing Li<sup>1</sup>, Xia Xiao<sup>1</sup>, Tianyun Zhang<sup>2</sup>, Mikhail Bragin<sup>1</sup>, Bing Yan<sup>3</sup>, Caiwen Ding<sup>1</sup>, Sanguthevar Rajasekaran<sup>1</sup>

<sup>1</sup>University of Connecticut, <sup>2</sup>Cleveland State University, <sup>3</sup>Rochester Institute of Technology

10:00AM

5C.4

84 A Novel Stochastic LSTM Model Inspired by Quantum Machine Learning

Joseph Lindsay and Ramtin Zand

University of South Carolina

# **SESSION 6A**

#### Friday April 7

# **Design of Emerging Circuits & Systems**

Chair: Rasit Topaloglu, IBM

Co-Chair: Ujwal Radhkrishna, Texas Instruments Inc.

10:45AM

6A.1

#### An Area Efficient Superconducting Unary CNN Accelerator

Patricia Gonzalez-Guerrero, George Michelogiannakis, Kylie Huch, Nirmalendu Patra, Thom Popovici

11:05AM

6A.2

# A Novel Scalable Array Design for III-V Compound Semiconductor-based Non-volatile 91 Memory (UltraRAM) with Separate Read-Write Paths

Shamiul Alam<sup>1</sup>, Kazi Asifuzzaman<sup>2</sup>, Ahmedullah Aziz<sup>3</sup>

<sup>1</sup>University of Tennessee Knoxville, <sup>2</sup>Oak Ridge National Laboratory, <sup>3</sup>University of Tennessee, Knoxville

11:25AM

6A.3

# 20CHEN: Compression using Zero chain elimination and encoding to improve endurance of Non-volatile Memories

Nishant Bharti<sup>1</sup>, Arijit Nath<sup>2</sup>, Swati Upadhyay<sup>1</sup>, Hemangee Kapoor<sup>3</sup>

<sup>1</sup>IIT Guwahati, <sup>2</sup>IIT Guwahati, India, <sup>3</sup>Indian Institute of Technology Guwahati

11:45AM

6A.4

# A Polymorphic Electro-Optic Logic Gate for High-Speed Reconfigurable Computing Circuits

Venkata Sai Praneeth Karempudi, Sairam Sri Vatsavai, Ishan Thakkar, Todd Hastings University of Kentucky

# **SESSION 6B**

### Friday April 7

### **Novel AI Computing**

Chair: Hongyu An, Michigan Technological University

Co-Chair: Haowen Fang, Synopsys

10:45AM

6B.1

87 Spiking Domain Feature Extraction with Temporal Dynamic Learning

Honghao Zheng and Yang (Cindy) Yi Virginia Tech

11:05AM

6B.2

Moving Towards Game-Changing Technology: Fabrication and Application of HfO2 RRAM for In-Memory Computing

Kang Jun Bai<sup>1</sup>, Daniel Titcombe<sup>2</sup>, Jack Lombardi<sup>1</sup>, Clare Thiem<sup>1</sup>, Nathaniel Cady<sup>2</sup>

<sup>1</sup>Air Force Research Laboratory, <sup>2</sup>SUNY Polytechnic Institute

11:25AM

6B.3

Cache Register Sharing Structure for Channel-level Near-memory Processing in NAND Flash Memory

133 HyunWoo Kim<sup>1</sup>, Seungwon Baek<sup>1</sup>, Minyoung Jung<sup>2</sup>, Jaehong Song<sup>1</sup>, Hyodong Kim<sup>1</sup>, Junhyeon Kim<sup>1</sup>, Seongju Kim<sup>1</sup>, Taigon Song<sup>1</sup>, Jongbeom Kim<sup>1</sup>, Hyundong Lee<sup>3</sup>, Yunjeong Go<sup>3</sup>

<sup>1</sup>Kyungpook National University (KNU), <sup>2</sup>Kyungpook National University (KNU),, <sup>3</sup>Kyungpook National University

11:45AM

6B.4

73 Online Training from Streaming Data with Concept Drift on FPGAs

Esther Roorda and Steve Wilton

University of British Columbia

# **SESSION 6C**

### Friday April 7

### **Security for Resource-Limited Devices**

Chair: Ava Hedayatipour, California State University, Long Beach

10:45AM

6C.1

# Attacks on Continuous Chaos Communication and Remedies for Resource Limited Devices

179 Device

Rahul Vishwakarma¹, Ravi Monani², Amin Rezaei², Hossein Sayadi², Mehrdad Aliasgari², Ava Hedayatipour³

<sup>1</sup>California State University Long Beach, <sup>2</sup>California State University, Long Beach, <sup>3</sup>CSULB

11:05AM

6C.2

Split-Slope Chaotic Map Providing High Entropy Across Wide Range

Partha Sarathi Paul<sup>1</sup>, Maisha Sadia<sup>1</sup>, Anurag Dhungel<sup>1</sup>, Parker Hardy<sup>1</sup>, Md Sakib Hasan<sup>2</sup>

<sup>1</sup>Graduate Student, <sup>2</sup>Assistant Professor

11:25AM

6C.3

Reconfigurable low-power Cryptographic processor based on LFSR for Trusted IoT platforms

181 Mohamed El-Hadedy¹, Russell Hua², Kazutomo Yoshii³, Wen-mei Hwu⁴, Martin Marqala⁵

<sup>1</sup>CalPoly Pomona, <sup>2</sup>California State Polytechnic University, Pomona, <sup>3</sup>Argonne National Lab, <sup>4</sup>University of Illinois at Urbana-Champaign, <sup>5</sup>University of Louisiana at Lafayette

11:45AM

6C.4

Automating Hardware Trojan Detection Using Unsupervised Learning: A Case Study

# 180 of FPGA

Jaya Dofe<sup>1</sup>, Shailesh Rajput<sup>2</sup>, Wafi Danesh<sup>3</sup>

<sup>1</sup>California State University, <sup>2</sup>California State University Fullerton, <sup>3</sup>University of Missouri, Kansas City

# CALL FOR PAPERS

# 25<sup>th</sup> International Symposium on

# **QUALITY ELECTRONIC DESIGN**

March 2024. Santa Clara, CA

Paper Submission Deadline: Sept. 9, 2023

Acceptance Notifications: Dec. 5, 2023 Final Camera-Ready paper: Jan. 10, 2024

A pioneer and leading interdisciplinary electronic design and semiconductor conference ISQED accepts and promotes papers in following areas:

- IoT and Cyber-Physical systems

- Cognitive Computing in Hardware

- IP Design, quality, interoperability and reuse

- Advanced 3D ICs & 3D Packaging

- FPGA Architecture, Design, and CAD

- Robust & Power-conscious Circuits & Systems

- Advanced & 3D IC Packaging Technology

- Hardware Security

- PCB and PWB Technology & Manufacturing

- Circuit & System Design

- EDA Methodologies, Tools, Flows

- **Semiconductor & Nano Technology**

- Test & Verification

- Design for Test

ISQED papers have been published in IEEE Xplore and conference proceedings and indexed in Scopus and El.

IC DESIGN & TEST

RESOURCES & LOGISTICS

www.InnovoTek.com